碩士學位論文

ICP Nitride를 이용한 비휘발성

강유전체 기억소자용 MeFINS 캐퍼시터 연구

(Study of MeFINS Capacitors for Non-Volatile

Ferroelectric Memory Device with ICP Nitride Treatment)

國民大學校 大學院 金屬材料工學科

閔 炯 燮

2001

ICP Nitride를 이용한 비휘발성

강유전체 기억소자용 MeFINS 캐퍼시터 연구

(Study of MeFINS Capacitors for Non-Volatile

Ferroelectric Memory Device with ICP Nitride Treatment)

指導敎授 金志泳

이 論文을 碩士學位 請求論文으로 提出함 2001年 12月

國民大學校 大學院 金屬材料工學科

閔 炯 燮

2001

閔 炯 燮 의

碩士學位 請求論文을 認准함

2001년 12월

審査委員長 이 재 갑 印 審査委員 정 우 광 印 審査委員 김 지 영 印

國民大學校 大學院

국 문 초 록

최근 휴대용 전자제품의 중요성이 더욱 증가하는 가운데 저전압 동 작에서도 우수한 영구분극 특성을 나타내는 NDRO(Non-Destructive Read-Out)형 FeRAM의 MeFIS 구조 캐퍼시터 연구가 국내외적으로 활발히 진행되고 있다. 그러나 PZT와 SBT 등의 강유전체는 고온 산 화 분위기의 결정화 열처리를 거쳐야만 강유전성을 나타내기 때문에 이에 따른 금속산화물과 Si 기판간에 생성되는 SiOx 등의 저유전율의 Si 산화물 형성으로 인하여 capacitence 저하와 더불어 금속의 Si 계면 으로의 확산으로 인하여 FET의 캐퍼시턴스 channel이 형성되는 Si 계 면의 특성 열화 현상이 문제시되고 있다. 이런 문제를 Si 기지 위에 매 우 얇은 극박막 nitride 층을 형성시켜, 고온 산화 분위기의 결정화시 원하지 않는 Si 산화물 계면층 형성을 억제할 수 있는 새로운 MeFINS(Metal/Ferroelectric/Insulator/Nitride/Semiconductor) 구조를 제안한다.

(100) 방향의 n-type Si wafer를 RCA 세정법을 이용하여 유기물 및 native oxide를 제거하고 ICP(Inductively Coupled Plasma)를 통해 nitride를 형성시킨 후 insulator로 반응성 스퍼터링으로 증착고 결정화 를 위한 열처리를 산소분위기에서 행하였다. 강유전체 박막은 spin coater을 이용한 sol-gel법으로 도포한 후 산소 분위기에서 결정화 열 처리하였다. 상부 전극은 shadow mask를 이용하여 2.0×10-4cm2로 형 성하였다. 강유전체는 대표적인 PZT와 SBT를 사용하였고 insulator로 PZT의 경우 TiO2를 SBT의 경우 Ta2O5를 이용하였다.

ICP Nitride 결과 Nitride의 두께는 43Å 정도이고 EOT (Equivalent Oxide Thickness) 23Å 정도의 두께를 나타낸다. PZT/TiO2 구조의 캐 퍼시터에서 Nitride 처리를 실시하지 않은 경우보다 nitride 처리를 한 시편이 높은 캐퍼시턴스 값을 나타내었다. 또한 MeFIS 구조의 강유전 특성을 판단할 수 있는 memory window(ΔV) 값도 ±3V 동작에서 TiO2 400Å의 경우 MeFINS 구조의 캐퍼시터 경우(ΔV = 0.8)가 MeFIS 구조(ΔV = 0.6)의 시편보다 큰 값을 나타내었다. SBT/Ta2O5

구조 또한 nitride 처리를 한 경우가 비교적 높은 캐퍼시턴스 값을 나 타내었고 memory window(ΔV) 값은 ±3V 동작에서 Ta2O5 200Å의 경우 MeFINS 구조(ΔV = 1.36)가 MeFIS 구조(ΔV = 0.6)보다 큰 값 을 나타내었다.

List of Figures

Fig. 1 Schematic diagrams which show the structure of perovskite.(ABO3)

Fig 2. Polarization versus applied electric field characteristics for (a)linear dielectric (b) non-linear dielectric (c)ferroelectirc Fig. 3 Cross-section of non-volatiole memory device

(a)DRO-type (b)NDRO-type

Fig. 4 Ideal C-V curve of NDRO-type memory device

Fig. 5 The image of NDRO FRAM structure with nitride treatment.

Fig. 6 A schematic of the ICP System

Fig. 7 The C-V curves and leakage current density of the Pt/SiNX/Si stack dielectric film

Fig. 8 C-V curve of Au/TiO2/Nitride/Si nitridation time

Fig. 9 The comparison of the C-V curves and leakage current density of MeIS and MeINS structure

Fig. 10 The C-V curve of MINS with various TiO2 thickness (a) as-dep (b)500℃ annealing (c)700℃ annealing

Fig. 11-1 The C-V curve of MIS and MINS with Ta2O5(200Å) Fig. 11-2 The C-V curve of MIS and MINS with Ta2O5(400Å) Fig. 12 Depth profiles on the MIS and MINS capacitors

Characterized by Auger Electron Spectroscopy(AES) Fig. 13 The comparison of the C-V curves and leakage current

density of MeFINS

Fig. 14 Depth profile on the MFIS capacitors characterized by Auger electron spectroscopy (AES)

Fig. 15-1 The C-V curve of MFIS Device with Various Operrating Voltages (200Å, Ta2O5)

Fig. 15-2 The C-V curve of MFIS Device with Various Operrating Voltages (400Å, Ta2O5)

Fig. 15-3 The C-V curve of MFINS Device with Various Operrating Voltages (200Å, Ta2O5)

Fig. 15-4 The C-V curve of MFINS Device with Various Operrating Voltages (400Å, Ta2O5)

Fig. 15-5 The C-V curve of MFIS Device with Various Operrating Voltages

Fig. 16 The comparison of MeFINS and MeFINS device

Fig. 17 The comparison of leakage current density of MeFINS and MeFINS devices

Fig. 18 The comparison of the C-V curves between PZT and SBT based capacitors

차 례

국문 초록 ···ⅰ List of Figures ···ⅲ 차례 ···ⅴ

1. 서론 ···1

2. 이론 및 문헌조사 ···4

2.1 강유전체 ···4

2.2 강유전체를 이용한 비휘발성 기억소자 (FeRAM) ···8

2.3 강유전체 기억소자의 동작 ···8

2.3.1 DRO(Destructive Read-Out)형 기억소자의 동작 · ···8

2.3.2 NDRO(Non-Destructive Read-Out)형 기억소자의 동작 ·9 3. 실험방법 ···13

3.1 시편제작 ···13

3.2 측정방법 ···14

4. 결과 및 고찰 ···17

4.1 SiNX의 특성 ···17

4.2 MIS와 MINS capacitor 특성 비교 ···21

4.2.1 Au/TiO2/SiNX/Si의 특성 ···21

4.2.2 Pt/Ta2O5/SiNX/Si의 특성 ···23

4.3 PZT/TiO2 구조의 MeFINS 캐퍼시터의 특성 고찰 ···30

4.4 SBT/Ta2O5 구조의 MeFINS 캐퍼시터의 특성 고찰 · ···35

4.5 MeFINS 캐퍼시터의 비교 ···44

5. 결론 ···46

6. 참고문헌 ···49

Abstract ···52

감사의 글 ···54

1. 서론

오늘날에 있어서 notebook 컴퓨터와 이동전화기와 같은 고성능의 이 동형(mobile or portable) 전자제품에 대한 수요는 폭발적으로 급증하고 있으며, 시장에서의 이동형 전자제품의 중요성은 더욱 더 증가하게 될 전망이다. 이동형 전자제품의 작동은 제품 내에 탑재될 수 있는 작고 가벼운 전지(Battery)의 기전력에 의존하게 되기 때문에, 전원을 공급 하지 않아도 정보를 잃어버리지 않는 비휘발성(Non-volatile) 기억소자 가 DRAM과 SRAM보다 더욱 이동형 전자제품용 기억소자로 적합하 다. 비휘발성 소자 중에 EEPROM, Flash memory 등은 데이터 기록동 작(Write operation)을 위해서는 기존의 battery로는 제공하기가 어려운 고전압이 요구되며, 데이터 기록 횟수가 106 이하로 한정되어져 있기 때문에 이동형 전자제품용 embedded memory로는 부적당하다. 따라 서, 저전압·저전력용 비휘발성(Non-Volatile) 기억소자로서 강유전체 특유의 영구분극 현상을 응용한 강유전체 기억소자의 개발에 대한 연 구가 매우 활발하게 진행되고 있다.

직접 ferroelectric을 Si 기판 위에 집적시킨 MFSFET 효과를 최대한 으로 극대화하는 동시에, ferroelectrics와 Si의 반응을 피하며 charge injection 문제를 피하는 방법으로서 고유전율과 화학적 안정성을 가지 는 금속산화물의 절연체(Insulator)를 Si 기판과 ferroelectrics 사이에 증착하고, 그 위에 강유전체 박막을 형성하는 MeFIS (Metal/Ferroelectric/Insulator/Si) 구조가 제안되었으며, Perovskite계의 PZT(Pb(ZrTi)O3)와 Layered Perovskite계의 SBT(SrBi2Ta2O9) 등과 같

은 저전압 동작에서도 우수한 영구분극 특성을 나타내고 있는 대표적 인 강유전체 물질을 사용하여 NDRO형 FRAM의 MeFIS 구조 캐퍼시 터의 연구가 국내외적으로 적극적으로 진행되고 있다. 그러나, PZT 와 SBT 등의 강유전체는 고온 산화분위기에서의 결정화 과정을 반드 시 거쳐야만 강유전성을 나타내기 때문에, metal oxide로 형성된 insulator층으로 강유전체와 Si과의 직접적인 반응을 최소화할 수 있더 라도, 다음과 같은 큰 문제가 현안으로 대두되고 있다.

첫 번째 문제는 고온 산화 분위기의 결정화 열처리에 의하여 금속산 화물과 Si 기판간에 생성되는 SiOx 등의 저유전율의 Si 산화물 interface layer가 형성되는 것이다. 이와 같은 현상은 Si-interface layer의 계면상태를 열악하게 할 뿐 만 아니라 고유전율의 강유전체-중 간 유전율의 금속산화물-저유전율의 interface layer 3개 층으로 형성된 직렬 캐퍼시터를 구성하게 되어 강유전체의 영구분극의 반전을 위해서 gate에 가해지는 동작전압의 대부분이 SiOx 계면층과 금속산화물층에 걸리게 한다. 따라서, MFIS 캐퍼시터의 안정적인 동작과 저저압 동작 이 불가능하게 되기 때문에, 저유전층의 SiOx 층 형성의 적극적인 방지 방안과 높은 캐퍼시턴스와 우수한 확산방지기능을 할 수 있는 금속산 화물 형성의 최적화가 저전압 동작하에서 우수한 특성을 가지는 MFIS 캐퍼시터 개발을 위하여 선행되어 이루어져야 만 한다.

다른 문제는 기존에 제시된 MFIS 구조 캐퍼시터의 확산방지막용 insulator 재료로서 완벽한 특성, 즉 고온 산화 분위기에서 안정하여 확 산방지능력이 매우 우수하여 박막화가 가능하고 30이상의 상대유전율 을 가져 캐퍼시턴스가 커서 동작전압의 대부분을 강유전체에 가하게

하는 박막재료의 개발이 미흡한 상태이다. 특히, 강유전체 PZT경우에 Pb는 500℃의 열처리에서도 Si과 반응을 일으키는 것이 보고되었다.

따라서, 확산방지능력이 매우 우수하여 30nm이하의 두께와 동시에 높 은 유전율(εr>20)을 가지는 효과적인 확산방지막용 Metal oxide의 개 발이 시급하다.

위에서 문제들을 해결하기 위해서 Si 기지 위에 매우 얇은 nitride 층 을 형성하여 고온 결정화 열처리에 원하지 않는 Si 산화물 계면층의 형성을 억제하는 동시에 우수한 특성을 가지는 Si/Si3N4 계면에 의하여 channel이 형성되는 Si 계면의 상태를 향상하고자 연구를 행하였다.

2. 이론 및 문헌조사

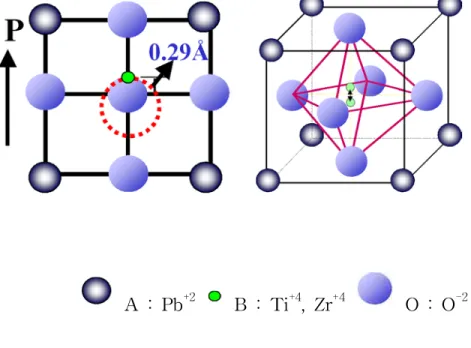

2. 1 강유전체절연체는 자유전자가 거의 존재하지 않으며 전기장이 인가되면 분극 화하여 전기 쌍극자를 발생시켜 흥미로운 전기적 특성을 나타낸다. 전 기 쌍극자는 전기장 뿐만 아니라 재료의 분자 구조에 의해서 영구히 분극이 생기는 존재가 있고 이들의 전기분극효과가 큰 재료를 유전체 (dielectric)라고 한다. 이런 유전체 중 유전상수가 크고 전계에 의해 반 전될 수 있는 자발분극을 갖는 물질을 강유전체(Ferroelectric)이라고 한다. 강유전체는 BaTiO3, PbTiO3, Pb(Zr, Ti)O3(PZT)와 같은 ABO3의 구조식을 갖는 페로브스카이트(Perovskite)구조를 갖는다. Fig. 1에서와 같이 페로브스카이트(Perovskite)구조는 원자반경이 큰 A원자는 단위포 모서리에 있고 원자반경이 작은 B원자는 체심에 있고 산소원자는 면심 에 위치한다. 또한, 작은 B원자는 산소원자의 팔면체자리에 위치한다.

PZT는 PbZrO3와 PbTiO3의 의사고용체(pseudo-solid solution)이다.

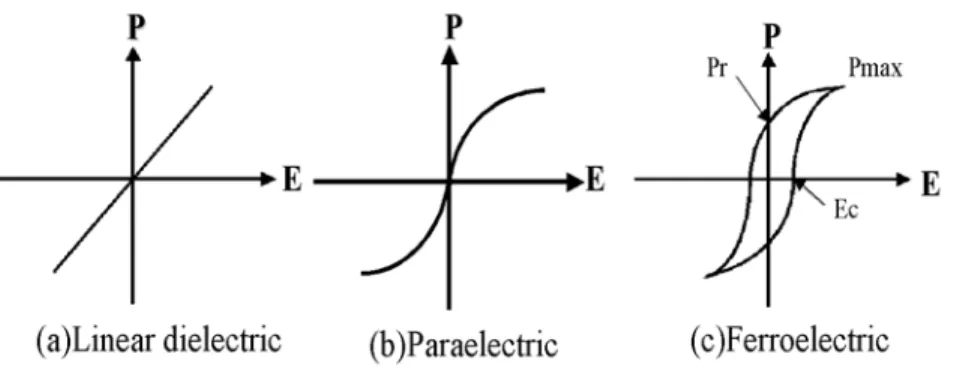

Ti+4 이온과 Zr+4 이온이 B원자 자리에 무질서하게 위치하고 있다. 고 온에서는 결정구조가 입방정인 상유전상으로 존재하며 상온에서는 조 성에 따라 결정구조가 사방정인 반강유전상, 능면체정인 강유전상, 그 리고 정방정인 강유전상으로 존재하며 Fig. 2에 나타내었다. PZT는 상 전이 온도가 높고 특정조성비에서 조성변화에 의한 상전이를 하며 정 방정상과 능면체정상이 경계영역(morphotropic phase boundary, MPB) 에서는 두상이 공존하며 유전율과 압전상수, 기계결합계수가 매우 크 다. 하지만, 강유전현상은 큐리천이온도 이상이 되면 사라지게 된다. 온

도가 증가함에 따라 열에너지에 의한 이온격자 내의 무질서도의 증가 가 강유전체의 이온들의 정렬성을 파괴하게 되므로 외부전압이 없어도 형성되었던 강유전체의 영구분극은 사라지게 되어 상유전체 상태가 된 다. 그림 2는 강유전체 물질과 비 강유전성을 나타내는 물질간의 Polarization과 Electric field와의 관계를 나타낸 그림이다.

A : Pb+2 B : Ti+4, Zr+4 O : O-2

Fig. 1 Schematic diagrams which show the structure of perovskite.(ABO3)

Fig 2. Polarization versus applied electric field characteristics for (a)linear dielectric (b) non-linear dielectric (c)ferroelectirc

2.2 강유전체를 이용한 비휘발성 기억소자 (FeRAM)

FeRAM이란 비휘발성 기억소자의 일종으로 기존 DRAM과 거의 같 은 구조를 갖는 기억소자이며, DRAM의 게이트 산화막 혹은 캐퍼시터 재료를 강유전체 재료로 대체하여 강유전체의 특성인 높은 잔류분극을 이용하여, 전계를 제거해도 저장된 정보가 지워지지 않는 기억소자를 말한다.

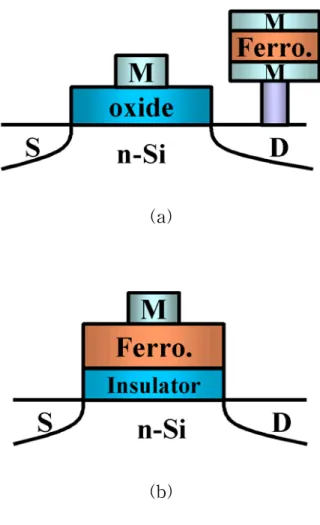

강유전체를 이용한 기억소자는 크게 두 가지로 대별될 수 있다. 파 괴적인 읽기 동작을 하는 Destructive read out (DRO)형과 비파괴적인 읽기 동작을 하는 Non-Destructive Read Out (NDRO)형으로 나눌 수 있고, 두 가지 구조에 대해 그림 3에서 나타내었다. DRO형은 기존의 MOSFET에 Stacked Ferroelectric Capacitor를 연결하여 데이터를 저 장하는 Dynamic Random Access Memory (DRAM)에서의 구조와 동 작원리가 유사하고, 일반적으로 1 Transistor - 1 Capacitor (1T-1C)의 구조를 가진다. NDRO형은 FET의 게이트에 강유전체 박막을 형성하 여 그 유전체의 잔류분극에 따른 FET 게이트의 문턱전압 (Threshold Voltage, VTh)을 변화시켜, Drain-Source 간의 conductance 변화를 통 하여 데이터를 읽을 수 있다.

2.3 강유전체 기억소자의 동작

2.3.1 DRO(Destructive Read-Out)형 기억소자의 동작

반전분극전류형 FRAM이라고도 불리는 DRO형 기억소자는 1

Transistor / 1 Capacitor 회로를 채용하고, Capacitor를 Transistor 위 에 형성하므로써 셀 면적을 줄여서 DRAM 수준의 집넉도를 기대할 수 있게 되었다. 이 형태의 FRAM의 동작원리를 그림 3에 나타내었다.

0, 1의 데이터를 쓰기 위해서는강유전체 캐퍼시터에 각각 +와 -의 항 전계를 인가한다. 한편 0의 데이터를 읽어낼 때는 +전계를 인가하며 이때의 분극량의 변화는 매우 작아 이 변화량으로부터 데이터가 0이었 음을 인식한다. 1의 데이터를 읽을 때도 +전계를 인가하나, 이때는 분 극 반전에 따른 분극량이 크므로 이 커다란 변화량으로부터 데이터가 1이었음을 인식한다. 단, 이 경우에는 그림에서 보듯이 데이터를 읽어 낸 후에는 데이터가 0상태가 되므로 초기의 데이터가 파괴된다. 따라 서 데이터를 읽은 후 곧바로 -의 전계를 인가하여 초기 상태로 데이터 를 재 기록할 필요가 있다.

2.3.2 NDRO(Non-Destructive Read-Out)형 기억소자의 동작

FET의 게이트 사이에 강유전체 막을 올려 그 강유전체의 자발 분극 의 방향에 따른 FET의 소스, 드레인간 체널의 컨덕턴스의 변화를 검 출하는 방식이다. 이 방식은 반전분극 전류형과는 달리 읽을 때 (read) 데이터의 파괴가 없고 쓰기(write) 동작에서도 역의 데이터를 읽기 동작을 할 때만 반전을 하기 때문에 강유전체 박막의 피로현상 (Fatigue)에 유리하다. 또한 캐퍼시터를 별도로 필요로 하지 않기 때 문에 소자의 구조를 보다 단순화시킬 수 있다는 장점이 있어 가장 이 상적인 FRAM이라고 할 수 있다.

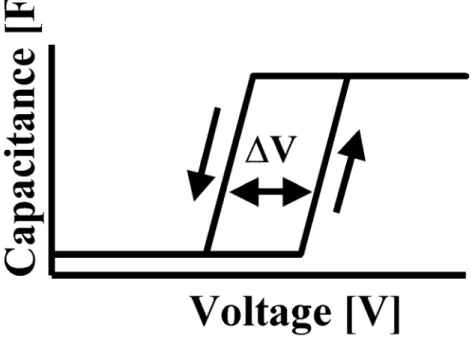

본 연구에서 제조한 MFIS 구조의 캐퍼시터는 NDRO형이고 이러한

구조의 소자 특성은 전압에 따른 캐퍼시턴스의 변화(C-V 곡선)를 관찰 함으로 알 수 있다. C-V 측정은 MOS 구조에서 행해지는 가장 기본 적인 측정중의 하나이며 절연 박막내의 oxide trapped charge, mobile ion, 계면에 인접한 fixed oxide charge, 계면의 interface trapped charge 등에 대한 중요한 정보를 알려준다. MOS 구조의 게이트에 dc bias를 인가하였을 때 bias에 따라 캐퍼시턴스가 변화하는데 이를 dc bias에 실린 작은 ac voltage를 이용하여 구할 수 있다. 그림 4는 n-type 기판을 사용한 게이트에 강유전체 층을 삽입한 MFS 구조의 이상적인 C-V곡선을 나타내고 있다. C-V측정결과 이력곡선이 발생하 는 것은 문턱전압(Threshold Voltage ; ΔVTh)이 음(-)의 방향으로 이 동했기 때문이고, 이는 강유전체 물질을 이용한 기억소자의 정보가 휘 발되지 않음을 보이는 것이다.

(a)

(b)

Fig. 3 Cross-section of non-volatiole memory device (a)DRO-type (b)NDRO-type

Fig. 4 Ideal C-V curve of NDRO-type memory device

3. 실험방법

3.1 시편제작실험에 사용된 wafer는 P가 3×1015㎤ 도핑된 n-type의 (100) Si prime wafer를 사용하여 RCA cleaning법으로 세정하였다. 이렇게 세 정된 시편을 ICP (Inductively Coupled Plasma) chamber에 즉시 장입 한다. 본 연구에서 행해진 Nitirdation 조건은 2×10-6Torr이하의 초기 진공에 substrate의 온도는 110℃로 유지한 후 99.9999%의 질소를 40sccm를 유입하여 6m torr의 공정압력에서 RF 전압으로 forward power 600W, bias power 50W로 5분간 doping하였다. 이후 완충층으 로 사용될 insulator 층은 99.9999%의 아르곤과 99.9999%의 산소를 혼 입하여 반응성 스퍼터링으로 증착이 되는데, 본 연구에서 행해진 증착 조건은 다음과 같다. 2×10-6Torr이하의 초기 진공을 유지한 chamber 에서 타겟과 기판의 거리가 6㎝이고, 공정압력은 8m torr의 공정압력에 서 하였고, TiO2 insulator의 경우 아르곤과 산소의 비가 17:3으로 120W의 DC power로 Ta2O5의 경우 아르곤과 산소의 비가 10:10으로 150W의 RF power로 증착하였다. 이렇게 형성된 insulator 층은 경우 에 따라 산소 분위기 하에서 결정화 열처리가 행해졌다. 열처리는 직 경이 3“인 관상로에서 산소 기체의 유량을 5 slm으로 하여 30분간 각 각의 온도에서 행하였다. 강유전체인 PZT와 SBT를 형성하기 위해 일본 고순도화학 연구소에서 개발되어 상용화된 sol-gel precursor를 이용하였고, 이 PZT precursor는 52 : 48의 Zr/Ti 원자 조성비를 갖는 다. insulator 층이 증착된 기판을 약 2000rpm의 속도로 회전시키고

그 위에 PZT solution을 떨어뜨려 1분간 회전 도포시킨다. PZT solution이 도포 된 기판을 10분간 150℃에서 건조시킨 후에 다시 10분 간 350℃에서 prebake한다. 이때 1회의 sol-gel 법에 의해 도포된 PZT 박막의 두께는 약 500Å이었고, 강유전체 박막의 두께는 도포 횟 수에 비례하게 되며 적당한 두께의 PZT 박막이 형성된 후에 비정질의 PZT 박막을 650℃, 산소분위기 하에서 30분간 결정화 열처리를 행하였 다. SBT precursor의 경우 Sr:Bi:Ta의 비율이 0.8:2.2:2의 원자 조성비 였고 1500rpm의 속도로 회전시킨 SBT solution이 도포된 기판을 5분 간 150℃에서 건조시킨 후에 다시 5분간 250℃에서 prebake하였고 2000Å SBT 박막을 형성 후 800℃, 산소분위기 하에서 1시간동안 결 정화 열처리를 행하였다.

캐퍼시터의 전기적 성질을 확인하기 위해 상부전극을 스퍼터링으로 형성하였으며, 전극 물질로는 Au, Pt를 shadow mask를 이용해 2×

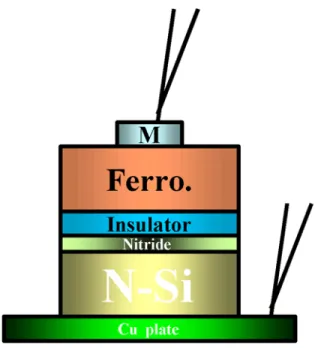

10-4㎠의 원형으로 제조하였으며, 약 2000Å 두께를 갖는다. Si 기지와 의 하부접촉을 위해 Si wafer 뒷면의 자연 산화막을 HF로 제거하고 Silver paste를 사용하여 구리 박판을 Si 뒷면에 접촉하여 하부전극을 형성하였다. 그림 5는 제조한 nitride 처리한 NDRO형 소자의 개략적인 구조이다.

3.2 측정방법

제작된 소자의 고주파 C-V 특성은 Hewlett Packard사의 HP4284A 를 사용하여 측정하였다. DC bias를 이용한 small signal frequency는

1MHz이고, small signal의 rms는 50mV, ramping speed는 0.05V/sec이 사용되었다. 누설전류의 특성은 Keithley 6517A를 이용하여 측정하였 다.

Fig. 5 The image of NDRO FRAM structure with nitride treatment.

4. 결과 및 고찰

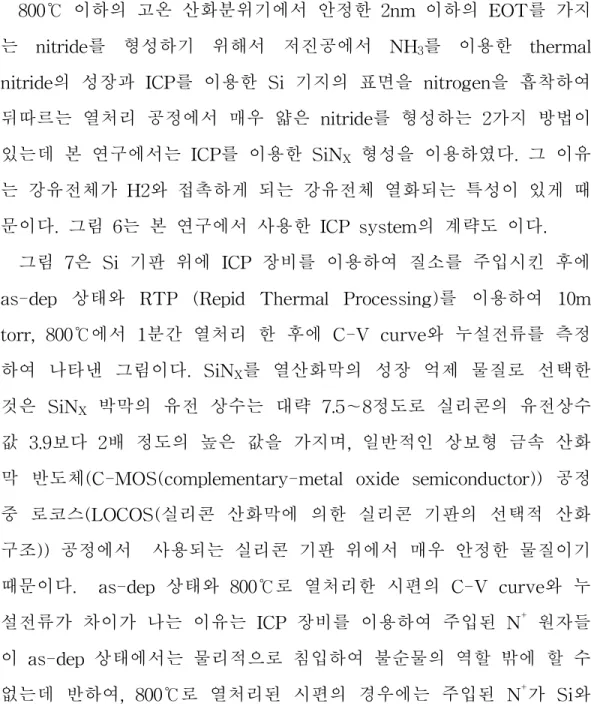

4.1 SiNX의 특성800℃ 이하의 고온 산화분위기에서 안정한 2nm 이하의 EOT를 가지 는 nitride를 형성하기 위해서 저진공에서 NH3를 이용한 thermal nitride의 성장과 ICP를 이용한 Si 기지의 표면을 nitrogen을 흡착하여 뒤따르는 열처리 공정에서 매우 얇은 nitride를 형성하는 2가지 방법이 있는데 본 연구에서는 ICP를 이용한 SiNX 형성을 이용하였다. 그 이유 는 강유전체가 H2와 접촉하게 되는 강유전체 열화되는 특성이 있게 때 문이다. 그림 6는 본 연구에서 사용한 ICP system의 계략도 이다.

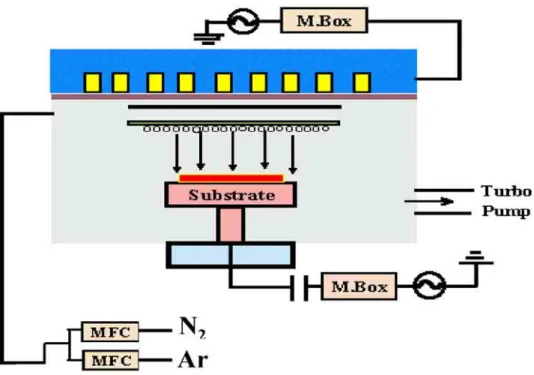

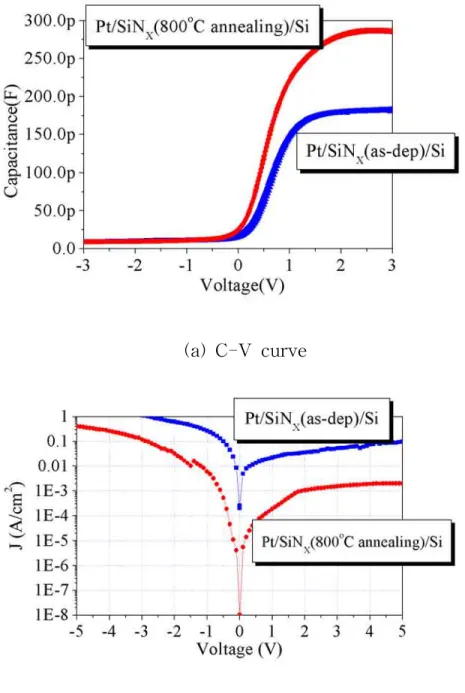

그림 7은 Si 기판 위에 ICP 장비를 이용하여 질소를 주입시킨 후에 as-dep 상태와 RTP (Repid Thermal Processing)를 이용하여 10m torr, 800℃에서 1분간 열처리 한 후에 C-V curve와 누설전류를 측정 하여 나타낸 그림이다. SiNX를 열산화막의 성장 억제 물질로 선택한 것은 SiNX 박막의 유전 상수는 대략 7.5∼8정도로 실리콘의 유전상수 값 3.9보다 2배 정도의 높은 값을 가지며, 일반적인 상보형 금속 산화 막 반도체(C-MOS(complementary-metal oxide semiconductor)) 공정 중 로코스(LOCOS(실리콘 산화막에 의한 실리콘 기판의 선택적 산화 구조)) 공정에서 사용되는 실리콘 기판 위에서 매우 안정한 물질이기 때문이다. as-dep 상태와 800℃로 열처리한 시편의 C-V curve와 누 설전류가 차이가 나는 이유는 ICP 장비를 이용하여 주입된 N+ 원자들 이 as-dep 상태에서는 물리적으로 침입하여 불순물의 역할 밖에 할 수 없는데 반하여, 800℃로 열처리된 시편의 경우에는 주입된 N+가 Si와

반응하여 SiNX을 형성할 수 있는 충분한 활성화 에너지를 얻어서 불순 물로서 존재하는 것이 아니라 SiNX을 형성하여 높은 Capacitance 값을 나타내는 것으로 생각되어진다. 열처리한 시편의 경우 Capacitance 값 이 288pF으로 nitride의 두께는 43Å 정도이고 EOT (Equivalent Oxide Thickness) 23Å 정도의 값을 나타낸다. leakage current 특성 또한 열 처리한 시편이 그렇지 않은 시편보다 2 order 정도의 낮게 나타나 열 처리한 시편이 계면특성이 더욱 좋은 것을 알수 있다. 이것 또한 앞에 서 서술한 봐와 같이 Si에 N+ 원자들이 주입된 시편이 열처리를 통해 충분한 활성화 에너지를 얻어서 완전한 SiNX 층을 형성된 것으로 사료 된다.

Fig. 6 A schematic of the ICP System

(a) C-V curve

(b) Leakage current density

Fig. 7 The C-V curves and leakage current density of the Pt/SiNX/Si stack dielectric film

4.2 MIS와 MINS capacitor 특성 비교

4.2.1 Au/TiO2/SiNX/Si의 특성

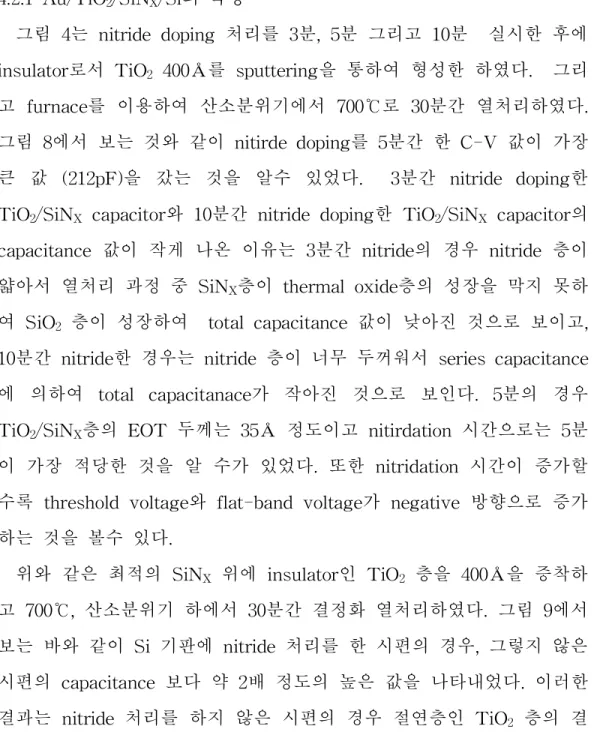

그림 4는 nitride doping 처리를 3분, 5분 그리고 10분 실시한 후에 insulator로서 TiO2 400Å를 sputtering을 통하여 형성한 하였다. 그리 고 furnace를 이용하여 산소분위기에서 700℃로 30분간 열처리하였다.

그림 8에서 보는 것와 같이 nitirde doping를 5분간 한 C-V 값이 가장 큰 값 (212pF)을 갔는 것을 알수 있었다. 3분간 nitride doping한 TiO2/SiNX capacitor와 10분간 nitride doping한 TiO2/SiNX capacitor의 capacitance 값이 작게 나온 이유는 3분간 nitride의 경우 nitride 층이 얇아서 열처리 과정 중 SiNX층이 thermal oxide층의 성장을 막지 못하 여 SiO2 층이 성장하여 total capacitance 값이 낮아진 것으로 보이고, 10분간 nitride한 경우는 nitride 층이 너무 두꺼워서 series capacitance 에 의하여 total capacitanace가 작아진 것으로 보인다. 5분의 경우 TiO2/SiNX층의 EOT 두께는 35Å 정도이고 nitirdation 시간으로는 5분 이 가장 적당한 것을 알 수가 있었다. 또한 nitridation 시간이 증가할 수록 threshold voltage와 flat-band voltage가 negative 방향으로 증가 하는 것을 볼수 있다.

위와 같은 최적의 SiNX 위에 insulator인 TiO2 층을 400Å을 증착하 고 700℃, 산소분위기 하에서 30분간 결정화 열처리하였다. 그림 9에서 보는 바와 같이 Si 기판에 nitride 처리를 한 시편의 경우, 그렇지 않은 시편의 capacitance 보다 약 2배 정도의 높은 값을 나타내었다. 이러한 결과는 nitride 처리를 하지 않은 시편의 경우 절연층인 TiO2 층의 결

정화 열처리 시에 Si와 절연체 층 사이에 열산화 막인 SiO2 층이 얇은 두께로 생기에 되어 전체적인 capacitance 값을 감소시키는 것으로 분 석되었다.

이러한 결정화 열처리 과정에서 생성될 수 있는 SiO2를 계산에 의해 구해 보았다. TiO2의 유전율을 50이라고 가정하고

1

C

Tot= 1

C

SiO2+ 1

C

TiO2 식을 이용하여 계산을 해보면, 식C = ε

0ε

rA d

을 이용하여 전극 면적 A와 두께 d, 캐퍼시턴스 C를 알고 있으므로 이 상적인 MIS 구조의 capacitance 값은 258pF이다. 따라서 위의 식에 넣어 계산하면 18Å 두께의 SiO2 층이 생성됨을 알 수 있다. 이러한 열산화 층의 형성을 nitride 처리를 실시함으로서 직렬 캐퍼시터(series capacitor)로 인한 capacitance의 감소가 거의 없이 이상적인 MIS 구조 의 소자를 형성할 수 있다. 그리고 또한 이때 형성된 SiNX은 약 10Å 정도로 계산되었다.

leakage current density 특성 또한 Si 기판에 nitride 처리를 한 시편 의 경우, 그렇지 않은 시편보다 2 order 정도의 좋은 특성을 나타내고 있다. 그림 10은 TiO2의 두께에 따라서 C-V 특성을 나타낸 것인데 열처리 온도가 올라감에 따라서 capacitance 값이 증가하는 것을 알 수 있고 또한 hysteresis loop(charge injection)가 감소하는 것을 알 수가 있다. 다른 한편 hysteresis curve의 크기는 TiO2의 두께에 의존하지 않는 것을 알 수 있다. 특히 as-dep과 500℃ 열처리한 것보다 700℃

에서 열처리한 시편이 급격한 capacitnace의 증가로 나타나는데 이것은 TiO2 층이 amorphous phase에서 anatase phase을 변화하면서 이에 따 른 유전율이 크게 증가하기 때문이다. 이것으로 TiO2/SiNX 층은 적당

한 열처리가 필요하다는 것을 알 수 있다.

4.2.2 Pt/Ta2O5/SiNX/Si의 특성

앞서 실험한 최적의 조건인 SiNX 층위에 절연체인 Ta2O5 층을 각각 200Å, 400Å을 증착하고 800℃, 산소분위기에서 30분간 결정화 열처리 하였다. 그림 11에서 보는 바와 같이 TiO2/SiNX와 비슷한 결과로 Si 기판에 nitride 처리를 한 시편의 경우, 그렇지 않은 시편의 capacitance 보다 약 2배 정도의 높은 값을 나타내었다. 이러한 결과는 nitride 처 리를 하지 않은 시편의 경우 절연층인 Ta2O5 층의 결정화 열처리 시에 Si와 절연체 층 사이에 열산화막인 SiO2 층이 얇은 두께로 생기에 되 어 전체적인 capacitance 값을 감소시키는 것으로 분석되었다. ICP nitridation과 800℃ 열처리한 시편이 높은 capacitance와 charge injection이 감소하는 것으로 보아 insulator의 적절한 열처리가 필요한 것을 알수 있었다. 그림 12는 AES depth profile로 Si 기판에 nitride 처리를 한 시편의 경우, 그렇지 않은 시편을 비교한 것인데 여기에서 nitride 처리한 AES depth profile이 결과를 보면 Si과 insulator인 Ta2O5사이에 질소(N)가 형성되어있는 것을 알 수 있다.

Fig. 8 C-V curve of Au/TiO2/Nitride/Si nitridation time

Fig. 9 The comparison of the C-V curves and leakage current density of MeIS and MeINS structure

(a)

(b)

(c)

Fig. 10 The C-V curve of MINS with various TiO2 thickness (a) as-dep (b)500℃ annealing (c)700℃ annealing

Fig. 11-1 The C-V curve of MIS and MINS with Ta2O5(200Å)

Fig. 11-2 The C-V curve of MIS and MINS with Ta2O5(400Å)

Fig. 12 Depth profiles on the MIS and MINS capacitors Characterized by Auger Electron Spectroscopy(AES)

4.3 PZT/TiO2 구조의 MeFINS 캐퍼시터의 특성 고찰

강유전체 PZT의 insulator로 Al2O3, ZrO2, TiO2, ZT, Ta2O5, 중 절연 산화막으로 유전율이 두께에 따라서 38.4∼56.8으로 높고 Pb의 확산을 막을 수 있고 PZT의 Ti와 호환성이 있는 TiO2를 선택하였다. TiO2의 두께는 Sputter를 이용하여 400Å 증착 하였고, PZT는 Zr/Ti가 52/48 인 solution을 sol-gel 방법으로 2000Å형성하였다. ICP nitridation 영 향을 알아보기 위해서 700℃에서 열처리한 TiO2 Au/TiO2/SiNX/n-Si 구조 capacitor와 Au/TiO2/n-Si 구조 capacitor를 비교하였다. Si wafer 위에 증착한 TiO2를 700℃에서 열처리하면 유전상수가 50정도로 anatase phase을 상변화 한다는 것은 보고되고 있다. 만약 interfacial 층이 없고 TiO2의 유전상수 50을 가진다면 accumulation 영역에서의 capacitance 값은 233pF이다. 하지만 그림에서 보는 봐와 같이 TiO2

400Å의 accumulation capacitance를 보면 128pF 정도로 이론적인 capacitance 값의 반정도 밖에 가지지 않는다. 다른 한편, ICP 처리한 TiO2/Nitride 구조의 capacitor는 215pF 정도로 이론적인 capacitance 값에 가까이 측정되었다. 이것은 높은 온도(700℃)에서 열처리하는 동 안 nitride 층이 열산화(thermal oxide)층의 생성을 막아주는 것을 의미 한다. 또한 열산화 형성을 억제하고 nitride 층을 활성화 할 수 있는 적 정 열처리 온도는 700℃인 것을 알 수 있다.

그림 18 는 MeFIS 구조(metal / ferroelectric / insulator / semiconductor)의 소자 중 nitride 처리 후 TiO2의 절연체와 강유전체 로 PZT를 이용한 capacitor 결과를 서로 비교하였다. Nitride 처리를

실시하지 않은 시편의 경우 전체적인 capacitance 값은 65pF 정도로 나타났지만 nitride 처리를 한 시편의 경우 125pF 정도의 비교적 높은 capacitance 값을 나타내었다. 이러한 결과 역시, SiNX의 형성으로 인 하여 절연체 층인 TiO2 층의 결정화 시, 또는 강유전체 층인 PZT 층 의 결정화 열처리 시에 생겨날 수 있는 열산화 층인 SiO2의 성장이 억 제됨으로 인하여 저 유전 물질인 SiO2의 직렬 캐퍼시터 효과에 의한 capacitance의 감소를 방지하였기 때문으로 분석되어진다. 또한 MeFIS 구조의 강유전 특성을 판단할 수 있는 memory windows(ΔV) 값도 ± 3V operating voltage에서 TiO2 400Å의 경우 nitride 처리를 실시한 경 우(ΔV = 0.8)가 nitride 처리를 실시하지 않은 경우(ΔV = 0.6)의 시편 보다 큰 값을 나타내었다. 또한 leakage current density도 nitride 처 리한 capacitor가 1 order 정도 낮은 것으로 보아 MeFINS 구조의 capacitor가 더 좋은 특성을 가지는 것을 알 수 있다.

그림 13 은 MeFINS 구조의 시편에 대한 AES 분석 결과이다. 일반 적인 TiO2를 절연층으로 사용하는 MeFIS 구조의 시편의 경우 Pb의 Si 로의 확산을 막을 수 있는 TiO2 절연층의 두께는 앞서 언급하였듯이 대략 1000Å 이상의 두께를 가져야 한다고 연구되어졌으나, nitride 처 리를 실시한 시편의 경우 400Å의 TiO2의 절연층과 약 43Å정도의 nitride 층에 의해서 Pb의 Si 기판으로의 확산을 충분히 막을 수 있었 다. 이러한 이유는 비교적 엉성한 구조인 TiO2 구조에 비해서 매우 치밀하고 밀도가 높은 SiNX 층의 형성이 Pb의 Si 기판으로의 확산을 억제하는 것으로 판단되어진다. 비교적 얇은 두께의 SiNX 층이지만 Si 기판과의 좋은 계면 특성과 치밀한 막질로 인하여 적은 양의 두께로도

확실하게 Pb의 Si로의 확산을 억제함을 확인할 수 있었다.(그림 14)

Fig. 13 The comparison of the C-V curves and leakage current density of MeFINS

Fig. 14 Depth profile on the MFIS capacitors characterized by Auger electron spectroscopy (AES)

4.4 SBT/Ta2O5 구조의 MeFINS 캐퍼시터의 특성 고찰

강유전체 SBT에는 insulator로 Al2O3, ZrO2, TiO2, ZT, Ta2O5, 중 절 연 산화막으로 유전율이 두께에 따라서 25.2으로 높고 Bi의 확산을 막 을 수 있고 SBT의 Ta과 호환성이 있는 Ta2O5를 선택하였다. Ta2O5

의 두께는 Sputter를 이용하여 200∼400Å 증착하였고, SBT solution은 sol-gel 방법으로 2000Å형성하였다. ICP nitridation 영향을 알아보기 위해서 산소분위기에서 1시간 동안 800℃에서 열처리한 Ta2O5

Pt/Ta2O5/Nitride/n-Si 구조 capacitor와 Pt/Ta2O5/n-Si 구조 capacitor 를 비교하였다. Si wafer 위에 증착한 Ta2O5를 800℃에서 열처리하면 유전상수가 50정도로 phase을 상변화 한다는 것은 보고되고 있다.

그림 11에서 보여진 것 같이 nitride 처리 후 열처리한 Pt/Ta2O5/SiNX/n-Si 구조 capacitor가 그렇지 않은 Pt/Ta2O5/n-Si 구조 capacitor 보다 큰 capacitance 값을 가는 것을 알 수 있다. 이것은 높 은 온도(800℃)에서 열처리하는 동안 nitride 층이 열산화(thermal oxide)층의 생성을 막아주는 것을 의미한다. 또한 열산화 형성을 억제 하고 nitride 층을 활성화 할 수 있는 적정 열처리 온도는 800℃인 것 을 알 수 있다.

그림 15은 MeFIS 구조(metal / ferroelectric / insulator / semiconductor)의 소자 중 nitride처리 후 Ta2O5의 절연체와 강유전체 로 SBT를 이용한 capacitor의 voltage 별로 측정한 결과이다. Nitirde 처리한 소자는 operating voltage에 따라서 memory widows가 점점 증 가함을 알 수 있다. 그러나 그렇지 않은 소자는 operating voltage에 따

라서 memory widows가 의존하지 않는 것을 알수 있다. 이것은 더 많은 연구가 필요하겠지만 charge injection이 원인으로 의미하고 있 다.

그림 16은 MeFIS 구조(metal / ferroelectric / insulator / semiconductor)의 소자 중 nitride처리 후 Ta2O5의 절연체와 강유전체 로 SBT를 이용한 capacitor 결과를 서로 비교하였다.

Nitride 처리를 실시하지 않은 시편의 경우 전체적인 capacitance 값 은 60pF 정도로 나타났지만 nitride 처리를 한 시편의 경우 86pF 정도 의 비교적 높은 capacitance 값을 나타내었다. 이러한 결과 역시, SiNX의 형성으로 인하여 절연체 층인 Ta2O5 층의 결정화 시, 또는 강 유전체 층인 SBT 층의 결정화 열처리 시에 생겨날 수 있는 열산화 층 인 SiO2의 성장이 억제됨으로 인하여 저 유전 물질인 SiO2의 직렬 캐 퍼시터 효과에 의한 capacitance의 감소를 방지하였기 때문으로 분석되 어진다. 또한 MeFIS 구조의 강유전 특성을 판단할 수 있는 memory windows(ΔV) 값도 ±3V operating voltage에서 Ta2O5 200Å의 경우 nitride 처리를 실시한 경우(ΔV = 1.36)가 nitride 처리를 실시하지 않 은 경우(ΔV = 0.6)의 시편보다 큰 값을 나타내었다.

Insulator의 두께가 감소하면 Capacitance 값이 증가하고 memory widows 또한 증가하는 것을 알수 있다. 이것은 insulator의 두께가 감 소하면 스위칭시에 강유전체 층에 충분한 전압이 인가되어, 소자가 정 확한 동작을 할 수 있게 한다.

Leakage current density는 SBT/Ta2O5/SiNX와 SBT/Ta2O5 capaitor 그림 17에서 보는 거와 같이 많은 차이는 나타내지는 않았다.

Fig. 15-1 The C-V curve of MFIS Device with Various Operrating Voltages (200Å, Ta2O5)

Fig. 15-2 The C-V curve of MFIS Device with Various Operrating Voltages (400Å, Ta2O5)

\

Fig. 15-3 The C-V curve of MFINS Device with Various Operrating Voltages (200Å, Ta2O5)

Fig. 15-4 The C-V curve of MFINS Device with Various Operrating Voltages (400Å, Ta2O5)

Fig. 15-5 The C-V curve of MFIS Device with Various Operrating Voltages

Fig. 16 The comparison of MeFINS and MeFINS device

Fig. 17 The comparison of leakage current density of MeFINS and MeFINS devices

4.5 MeFINS 캐퍼시터의 비교

그림 18은 Au/PZT/TiO2/SiNX/n-Si 소자 capacitor와 Pt/SBT/Ta2O5/SiNX/n-Si 소자 capacitor를 비교하여 하였다.

PZT/TiO2/SiNX 소자의 경우 SBT/Ta2O5/SiNX 소자 보다 C-V curve 가 기울어 있고 threshold voltage와 flat-band voltage가 negative voltage에 이동되어 있는 것으로 보아서 PZT/TiO2/SiNX 소자가 SBT/Ta2O5/SiNX 소자보다 상대적으로 interface state density가 나쁘 다는 것을 알 수 있다. 그러나 total capacitance 값은 PZT/TiO2/SiNX

소자 capacitor 경우 123pF 정도이고 SBT/Ta2O5/SiNX 소자 capacitor 의 경우 83pF으로 보다 높게 나왔다. 이것은 강유전체의 유전율의 차 이에 의해서 이런 결과가 나왔다고 생각된다. PZT가 SBT보다 유전율 이 훨씬 크기 때문이다. 하지만 memory windows 경우는 반대로 SBT/Ta2O5/SiNX 소자 capacitor가 PZT/TiO2/SiNX 소자 capacitor보다 크게 나타난 것으로 보아 종합적으로 볼 때 PZT/TiO2/SiNX 소자 capcitor보다 SBT/Ta2O5/SiNX 소자 capacitor가 좋은 결과를 보였다.

Fig. 18 The comparison of the C-V curves between PZT and SBT based capacitors

5. 결론

본 연구에서는 nitride을 이용하여 새로운 MeFINS 구조로 구성된 소 자에 있어서, 절연층과 실리콘 웨이퍼 사이의 계면에 강유전체 층, 또 는 절연체 층의 결정화 열처리 시에 형성되는 열산화(thermal oxide)로 인한 직렬 캐패시터 구조의 형성으로 인한 캐패시턴스의 감소로 인한 특성 변화를 ICP 장비를 이용하여 Si 계면과 절연층 사이에 형성되는 열산화층의 성장을 억제할 수 있는 SiNX를 형성하여 그 전기적인 특성 과 구조 (metal/ferroelectric/insulator/nitride/semiconductor)의 안정성 을 연구하였다.

ICP nitirdation capacitor의 RTP 열처리한 시편의 경우 Capacitance 값이 288pF으로 nitride의 두께는 43Å 정도이고 EOT (Equivalent Oxide Thickness) 23Å 정도의 값을 나타낸다. 또한 SiNX과 Si 기판 간의 계면특성도 상당히 우수한 것으로 판단되었다.

MeFIS 구조(metal / ferroelectric / insulator / semiconductor)의 소 자를 형성하여 nitride 처리를 실시하여 특성을 연구하였다. Nitride 처 리를 실시하였을 경우 그렇지 않은 시편의 경우보다 매우 높은 capacitance, memory window 값을 나타내었다. 이러한 결과는 nitride 처리를 실시함으로써 강유전체의 결정화 열처리 과정에 생겨날 수 있는 저유전율의 열산화막의 성장을 억제함으로써 실제적인 강유전 체 층에 작용하는 전압을 증가시키기 때문인 것으로 판단되어진다. 또 한, insulator 층의 두께가 감소함에 따라서 높은 capacitance를 얻을 수 있었다.

PZT/TiO2 구조의 capaitor에서 Nitride 처리를 실시하지 않은 시편의 경우 전체적인 capacitance 값은 65pF 정도로 나타났지만 nitride 처리 를 한 시편의 경우 125pF 정도의 비교적 높은 capacitance 값을 나타 내었다. 이러한 결과 역시, SiNX의 형성으로 인하여 절연체 층인 TiO2

층의 결정화 시, 또는 강유전체 층인 PZT 층의 결정화 열처리 시에 생 겨날 수 있는 열산화 층인 SiO2의 성장이 억제됨으로 인하여 저 유전 물질인 SiO2의 직렬 캐퍼시터 효과에 의한 capacitance의 감소를 방지 하였기 때문으로 분석되어진다. 또한 MeFIS 구조의 강유전 특성을 판 단할 수 있는 memory window(ΔV) 값도 ±3V operating voltage에서 TiO2 400Å의 경우 nitride 처리를 실시한 경우(ΔV = 0.8)가 nitride 처 리를 실시하지 않은 경우(ΔV = 0.6)의 시편보다 큰 값을 나타내었다.

SBT/Ta2O5 구조의 Nitride 처리를 실시하지 않은 시편의 경우 전체 적인 capacitance 값은 60pF 정도로 나타났지만 nitride 처리를 한 시편 의 경우 86pF 정도의 비교적 높은 capacitance 값을 나타내었다. 이러 한 결과 역시, SiNX의 형성으로 인하여 절연체 층인 Ta2O5 층의 결정 화 시, 또는 강유전체 층인 SBT 층의 결정화 열처리 시에 생겨날 수 있는 열산화 층인 SiO2의 성장이 억제됨으로 인하여 저 유전 물질인 SiO2의 직렬 캐퍼시터 효과에 의한 capacitance의 감소를 방지하였기 때문으로 분석되어진다. 또한 MeFIS 구조의 강유전 특성을 판단할 수 있는 memory window(ΔV) 값도 ±3V operating voltage에서 Ta2O5

200Å의 경우 nitride 처리를 실시한 경우(ΔV = 1.36)가 nitride 처리를 실시하지 않은 경우(ΔV = 0.6)의 시편보다 큰 값을 나타내었다.

본 연구에서 제작한 Au/PZT/TiO2/SiNX/Si 과 Pt/SBT/Ta2O5/SiNX/Si

구조의 capacitor 모두 낮은 voltage(±3V)에 NDRO형 FeRAM으로 사 용 가능하다. 일반적으로 PZT가 SBT보다 더 큰 잔류 분극을 나타냄 에도 불구하고, SBT를 사용한 MeFINS는 PZT를 사용한 MeFINS 캐 퍼시터 보다 더 큰 memory widow를 나타내고 있는 동시에 accumulation에서 inversion으로 변하는 구간에서 더 큰 기울기의 C-V 곡선을 나타내고 있다. 이와 같은 원인의 주요 이유는 PZT의 Pb 성 분이 휘발성이 강하기 때문에 쉽게 Si 층으로 확산되어지는 동시에 너 무 큰 PZT의 유전상수 (즉, 캐퍼시턴스)로 인하여 gate에 인가된 전압 중에 실질적으로 강유전체에 작용하는 전압이 급격하게 감소되는 것이 중요 이유로 생각된다. 또한, PZT가 SBT보다는 저전압동작이 열약하 기 때문에 이와 같은 결과가 나타나는 것으로 여겨진다. 따라서, SBT 의 경우에는 비교적 높은 공정온도가 요구될지라도, Si과의 반응이 적 고, 저전압동작이 우수하기 때문에 NDRO형 FeRAM 게이트용 강유전 체로서 더욱 적합할 것으로 여겨진다.

Pt/SBT/Ta2O5/SiNX/Si 구조의 캐퍼시터는 본 연구의 최종 목표인 낮은 전압에서의 충분한 memory window확보와 더불어 낮은 계면상태 를 나타내는 우수한 C-V 곡선을 나타내었다. 이와 같은 우수한 특성 의 확보는 ICP를 이용하여 수소열화 현상이 없는 우수한 nitridation 기 법의 개발에 의해 이루어졌다.

6. 참고문헌

1. S. Kobayashi, K. Amanuma, and H. Hada, IEEE Electron Device Letters, Vol. 19, No. 11, pp. 417∼419 (1998)

2. M. S. Tsai, S. C. Sun, and T. Y-Tseng, IEEE Transactions On Electron Devices, Vol. 46, No. 9, pp. 1829 ∼1838 (1999)

3. K. K-Abdelghafar, H. Miki, F. Yano, and Y. Fujisaki, Jpn. J. Appl.

Phys., Vol. 36, pp. L1032∼L1034 (1997)

4. Shu-Yau Wu, IEEE Transactions On Electron Devices, Vol. ED-21, No.

8, pp. 499∼504 (1974)

5. S. M. Yoon, E. Tokumitsu, and H. Ishiwara, IEEE Electron Device Letters, Vol. 20, No. 5, pp. 229∼231 (1999)

6. S. B. Desu, H. S. Cho, and P. C. Joshi, Appl. Phys. Lett., Vol. 70 (11), pp. 1393∼1395 (1997)

7. J. S. Lyu, B. W. Kim, K. H. Kim, J. Y. Cha, and H. J. Yoo, IEDM 96-503∼506 (1996)

8. T. Hirai, Y. Fujisaki, K. Nagashima, H. Koike, and Y. Tarui, Jpn. J.

Appl. Phys., Vol. 36, pp. 5908∼5911

9. M. B. Lee, T. Ohnishi, T. Maeda, and M. Kawasaki, Jpn. J. Appl.

Phys., Vol. 36, pp. 6500∼6503 (1997)

10. T. Hirai, K. Nagashima, H. Koike, S. Matsuno, and Y. Tarui, Jpn. J.

Appl. Phys., Vol. 35, pp. 5150∼5153 (1996)

11. N. A. Basit, and H. K. Kim, Applied Physics Letters, Vol. 73, No. 26, pp. 3941∼3943 (1998)

12. Y. T. Kim, C. W. Lee, D. S. Shin, and H. N. Lee, IEDM, pp. 35∼38 (1998)

13. S. B. Desu and I. K. Yoo, Integrated Ferroelectrics, 3, 365, (1993).

14. I. K. Yoo, S. B. Desu and J. Xing, MRS Symp. Proc., ,310, 165, (1993).

15. W. Y. Pan, C. F. Yue and B. A. Tuttle, Ceram. trans, 25, 385, (1992).

16. J. F. Scott and C. A. Paz de Arajuo, Science, 246, 1400, (1989).

17. Leo N. Chapin and sharon A. Myers, Mrter. Res. Soc., 153, (1990).

18. C. V. R. Vasant Kumar and M. Sayer, J. Appl. Phys., 71, 864, (1992).

19. J. H. Joo and S. K. Joo, Extended Abs. of the 1995 Int. Conf. on Solid State Device and Materials, Osaka, 5124, (1995).

20. Jae-Hyun Joo, You-Jin Lee, Seung-Ki Joo, Ferroelectrics, 196, 1, 1997.

21. Jang-Sik Lee, Eung-Chul Park, Deok-Sin Kil, Kwang-Ho Kim, Byung-il Lee, Seung-Ki Joo, The 3rd international meeting of pacific rim ceramic society (KyungJu), 98. 9. 23, 1998.

22. 이장식, 박응철, 이병일, 주승기, “대한 금속.재료학회지, 38, 1, 148, 2000.

23. I. K. YooS. B. Desu and J. Xing, Materials Research Society Symposium, 310, 166, (!993).

24. D. M. Smith, Ferroelectrics, 116, 117, (1992).

25. R. Waser and M. Klee, Integrated Ferroelectrics 2, 23, (1992).

26. M. V. Raymond, J. Chen, and D.M. Smith, Integrated Ferroeceltrics, 83 (12), 7789, (1994).

27. J. A. Voigt, B. A. Tuttle, T. J. Headley and D. L. Lamppa, Materials Research Society Symposium Proc. 361, 395, (1995).

28. S. Kamiyama. et. al, IEDM Tech. Digest, 91-827(1991)

29. W/ L. Warren, D. Dimos, B. A. Tuttle and G. E. Pike, Appl. Phys.

Lett. 65(8), p.1018, (1994)

30. R. H. Dennard. "Field Effect Transistor Memory"(1968)

31. W. Regitz and J. A. karp. IEEE. Jour, Solid-State circuits.

SC-5. p.181(1970)

32. T. Nakamura, Y. Nakao, A. Kamisawa, and H. Takasu, IEDM, pp. 345∼347 (1995)

33. 오기영, 요업기술지, Vol. 11, No. 3, pp. 171∼183 (1996)

34. Ihasan Barin, Thermochemical Data of Pure Substance, VCH Verlags Gesel m.b.h., Weinheim, 1989.

35. Y. Xu, Ferroelectric Materials and their Applications, (North-Holland, 1991) Chap. 3, pp114.

36. Hyung-Seok Kim, Ilhwan Bang, Jiyoung Kim, "Electrical Properties of MFIS Capacitors with PZT/TiO2 Layers", J. Kor. Phys. Soc. Vol.35 p.S123 (1999)

Abstract

FET (Field-Effect-Transistor) type ferroelectric random access memory (FeRAM) recently attracts an attention for non-destructive read-out (NDRO) type nonvolatile memory applications with a low operation voltage. Ferroelectric thin films are directly employed as a gate dielectric, and a remnant polarization of the gate ferroelectric decides a channel conductance that represents memory status. However, it is very difficult to form the ferroelectric-semiconductor interface while keeping excellent electrical properties. MeFIS (Metal/Ferroelectric/ Insulator/Si) structure capacitors were proposed to avoid direct reaction between the ferroelectric and Si substrate. Even though the insulator layer reduces the interdiffusion, a higher operation voltage for MeFIS devices is required in order to supply enough voltage to ferroelectric layer because of a series capacitance effect than an expected voltage for ideal MFS (Metal/Ferroelectric/Si) FET operations. At the same time, undesirable Si oxide is formed between the insulator and the Si substrate during high temperature annealing for ferroelectric crystallization. The interfacial SiOX

brings on an additional series capacitors problem, which reduces total capacitance and an actual applying voltage on ferroelectrics. In addition, a large electric field applied on the interfacial SiOX frequently causes significant charge injection and reliability problems. Therefore, it is important to avoid formation of SiOX layer in order to reduce the series capacitance problem and to maintain high capacitance at the insulator layer.

Since Si3N4 is thermodynamically more stable than SiO2 and have a higher dielectric constant of 7.5 than that of oxide, NH3 treatments preventing undesirable oxide growth have been widely studied for alternative gate dielectric applications. However, processes involved with

hydrogen often cause a significant degradation of ferroelectric properties.

In this study, nitridation with pure N2 using ICP (Inductively Coupled Plasma) was evaluated as a hydrogen free process.

Since ICP nitridation is a physical process that provides activated nitrogen speices without thermal inputs, effects of annealing on characteristics of Metal/SiNX/Si structure capacitor are investigated in order to know the quality of the nitirde. Thickness of the nitride layer and EOT (Equivalent Oxide Thickness) of the annealed devices are about 4.9nm and 2.3nm. it is thought that the device has good interface properties between SiNX and Si substrate.

MeFINS (Au/PZT/TiO2/SiNX/Si) capacitors with show higher total capacitance than MeFIS capacitors without treatment. This implies that the suppression of oxide formation is achieved and the applying voltage on ferroelectrics layer is also higher. As a result, the MeFINS capacitors with ICP treatments exhibits wider memory window (△V =0.8V) than that of MeFIS (△V =0.6V) device. At the same time, the capacitance of the MeFINS device is almost twice higher than that of the MeFIS capacitor, because MeFINS capacitor has less significant series capacitor problem. Even if ICP nitridation treatments are performed, the capacitance and memory window are small when TiO2 layer is too thick.

Also, MeFINS(Pt/SBT/Ta2O5/SiNX/Si) capacitors with ICP nitrogen treatments show higher total capacitance than MeFIS capacitors without treatment. This implies that ICP nitridation successfully suppresses undesirable oxide formation even under extremely severe SBT annealing conditions and results in high actual applying voltage on ferroelectrics layer. As a result, the MeFINS capacitors with ICP treatments exhibits wider memory window (△V =1.36V) than that of MeFIS (△V =0.6V) device under ±3V sweeping voltage operation.

감사의 글

전자재료실험실(EML)에 들어 온지 어제 같은데 벌써 2년이라는 시간 이 정말 빠르게 흘러갔습니다. 뒤돌아보면 많은 후회와 미련이 남지만 제 인생에서 아주 소중한 시간이었던 것 같습니다. 새로운 출발의 시점 에서 많은 도움을 주신 분들께 이 미미한 글을 통해서나마 감사하는 마음을 전합니다. 먼저 부족한 저에게 공학도로서 논리적 사고와 자세 를 가르쳐 주시고 끊임없는 관심과 지도, 편달해 주신 김지영 지도교수 님에게 진심으로 감사를 드리고, 언제나 큰 관심과 가르침을 주신 이재 갑 교수님에게도 깊은 감사를 드립니다. 또한 대학원생활에 가르침을 주신 조남돈 교수님, 이진형 교수님, 박화수 교수님, 지충수 교수님, 권 훈 교수님, 김용석 교수님, 이재봉 교수님, 남원종 교수님, 정우광 교수 님, 이건배 박사님, 고연규 박사님, 이원희 박사님께 깊은 감사 드리고 과사무실에 계시는 김충서 누님에게도 감사하고 저에게 많은 관심과 격려를 주신 최 용 교수님, 이창순 교수님, 박인규 교수님께도 심심한 감사를 드립니다.

실험실의 맏형으로 모범을 보여준 준모형에게 진심으로 고맙고, 실험실 에 남아 있는 창배형, 주환이, 노헌이, 성호, 봉식이와 정성원 박사과정 님에게도 진심으로 고맙고, 고생한 만큼 좋은 결과 있길 바랍니다. 그 리고 반도체제조공정실험실의 친구이자 선배로서 많은 도움을 준 양희 정 박사과정에게 고마움을 느끼며, 봉주형, 종호형, 서범석이형, 두식이 형, 성진이, 현무, 섭이에게도 고맙다는 말을 전합니다.

나의 대학원 생활에 큰 도움이 되어준 준수, 도훈, 동구, 성철, 현국, 영

민이와 진수형과 강도방의 성하형에게도 고맙다는 말을 전합니다.

끝으로 이 세상에 제가 있을 수 있도록 나아주시고 키워주신 부모님과 누나, 매형 그리고 형에게 사랑한다는 말씀을 드리며 이 글을 마무리 하고자 합니다.