DOI : 10.5515/KJKIEES.2011.22.6.584

충남대학교 전파공학과(Department of Radio Science and Engineering, Chungnam National University)

․논 문 번 호 : 20110125-010

․교 신 저 자 : 김동욱(e-mail : dwkim21c@cnu.ac.kr)

․수정완료일자: 2011년 4월 8일

pHEMT 공정을 이용한 저손실, 고전력 4중 대역용 SP6T 스위치 칩의 설계 및 제작

Design and Fabrication of Low Loss, High Power SP6T Switch Chips for Quad-Band Applications Using pHEMT Process

권 태 민․박 용 민․김 동 욱

Tae-Min Kwon․Yong-Min Park․Dong-Wook Kim 요 약

본 논문에서는WIN Semiconductors사의 0.5 μm PHEMT 공정을 이용하여 GSM/EGSM/DCS/PCS 4중 대역을 위한 저손실, 고전력의 RF SP6T 스위치 칩을 설계, 제작 및 측정하였다. 스위치 특성을 개선시킬 수 있는 최적의 구조를 위해서series와 series-shunt 구조를 혼용하였고, 칩 크기를 줄이기 위해서 수신단에 공통 트랜지스터 구조 를 사용하였다. 또한, 시스템에 사용되는 ON, OFF 상태의 입력 전력을 고려하여 트랜지스터의 게이트 크기와 스택(stack) 수를 결정하였다. 마지막으로 피드 포워드(feed forward) 캐패시터, shunt 캐패시터 그리고 shunt 트랜 지스터의 기생 인덕턴스 공진 기법을 적용하여 격리도 및 전력 특성을 개선하였다. 제작된 스위치 칩의 크기는 1.2×1.5 mm

2

이며, S 파라미터 측정 결과 삽입 손실은 0.5~1.2 dB, 격리도는 28~36 dB를 보였다. 전력 특성으로는4 W의 입력 전력에 대해서도 삽입 손실 및 격리도의 특성 변화가 없었으며, 75 dBc 이상의 2차 및 3차 고조

파 억제 특성이 확보되었다.

Abstract

In this paper, low-loss and high-power RF SP6T switch chips are designed, fabricated and measured for GSM/

EGSM/DCS/PCS applications using WIN Semiconductors 0.5 μm pHEMT process. We utilized a combined configura- tion of series and series-shunt structures for optimized switch performance, and a common transistor structure on a receiver path for reducing chip area. The gate width and the number of stacked transistors are determined using ON/

OFF input power level of the transceiver system. To improve the switch performance, feed-forward capacitors, shunt capacitors and parasitic FET inductance elimination due to resonance are actively used. The fabricated chip size is 1.2×1.5 mm

2

. S-parameter measurement shows an insertion loss of 0.5~1.2 dB and isolation of 28~36 dB. The fabricated SP6T switch chips can handle 4 W input power and suppress second and third harmonics by more than 75 dBc.Key words : pHEMT, SP6T Switch, Quad Band, Feed Forward Capacitor

Ⅰ. 서 론

오늘날 전 세계적으로 다양한 휴대 통신 방식과

시스템이 사용되고 있으며, 기술의 발달로 인해 하 나의 단말기로 로밍을 통하여 대부분의 휴대 통신 시스템에 접속이 가능해졌다. 이는 휴대폰의RF 전

단부 부분에 위치하는ASM(Antenna Switch Module) 기술의 발전 결과라 할 수 있겠다. 따라서 ASM의 핵심 부품인RF 스위치 칩의 중요성이 커지고 있다. 본 논문에서는 GSM/EGSM/DCS/PCS의4중 대역에 서 사용 가능한 스위치 칩에 대해서 연구를 진행하 였다.

4중 대역용 TDMA 방식은 안테나와 6개의 송수 신 포트 사이의 원활한 연결을 위해서 복잡한 스위 칭을 요구하며, 안테나 바로 뒷단에 위치하여 송신 신호와 수신 신호를 제어하는RF 스위치를 필요로 한다. 스위치는 과거PIN 다이오드를 사용하여 제작 되었지만 휴대 통신이 더욱 복잡해지고 다중 대역으 로 발전하면서 현재는 트랜지스터 스위치로 대체되 었다. 다중 대역을 위해 포트가 늘어나게 되면 PIN 다이오드 스위치는 트랜지스터 스위치에 비해 삽입 손실이나 격리도 특성이 더욱 악화된다. 또한, 저전 류, 저전압 성능을 요구하는 현재의 시스템 규격에 의해 제한을 받게 된다. 따라서 본 논문에서는 작은 삽입 손실, 빠른 스위칭 속도, 넓은 대역폭 등의 강 점을 가지는 GaAs 기반의 pHEMT를 사용하여 4중 대역에서 저손실, 고전력 특성을 갖도록SP6T(Single Pole 6 Throw) RF 스위치를 설계 및 제작하였다

[1],[2]

.Ⅱ. 이론 및 설계

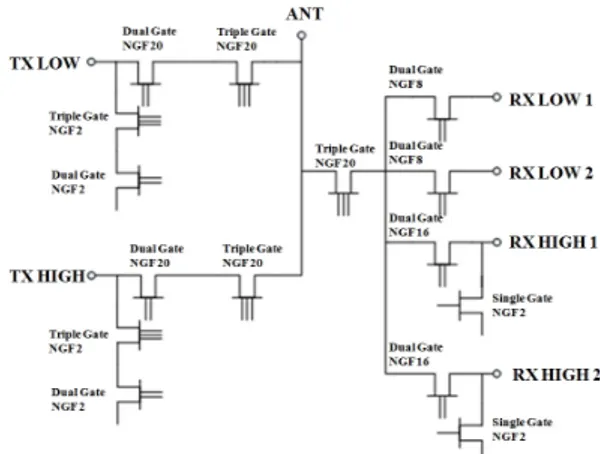

2-1 스위치 구조

스위치 설계에 있어서 적절한 스위치 구조의 선 택은 설계 규격을 고려하여 가장 먼저 진행해야 할 과정이다. 스위치 설계를 위해 사용되는 구조는seri- es, shunt 그리고series-shunt 크게3가지가 있다. Se-

ries 구조는 다른 구조와 비교해 간단하고 삽입 손실

이 좋은 특성을 가지며, series-shunt 구조는 격리도를 개선시킬 수 있는 장점을 가지고 있다. 따라서 본 논 문에서는series와series-shunt 구조를 혼용하여 스위 치 설계를 진행하였다. 송신단에는 송신단 사이의 격리도 특성을 고려하여 series-shunt 구조를 적용하 였고, 수신단의 경우GSM, EGSM의 저대역은 삽입 손실이 좋은series 구조를, DCS 및PCS의 고 대역은 격리도 특성에 따른 삽입 손실 악화를 최소화하기 위해서series-shunt 구조를 적용하였다. 또 수신단에 는 스위치 칩의 전체 크기를 줄이기 위하여 공통 트

그림 1. 설계된 SP6T 스위치 회로의 기본 구조 Fig. 1. The basic SP6T switch circuit structure.

랜지스터(FET A)로 수신단 전체를 묶어 설계하였다

[3]

. 그림1에 설계된 스위치 회로의 기본 구조를 나 타내었다.2-2 전력 능력(Power Handling)

원하는 시스템 입력 전력에 대해서 스위치가 충 분히 안정적으로 동작하기 위해서는 전력 특성을 고 려해 주어야 한다. 이를 고려해 주지 않으면 스위치 가 파손되거나 상태를 유지하지 못하는 오동작의 원 인이 된다. ON 상태에 대해서는 전력에 대한 전류

를, OFF 상태에 대해서는 전력에 대한 전압을 고려

해 주어야 한다. SP2T 회로에서ON 상태와OFF 상 태의 트랜지스터에 대한 신호 흐름을 그림2에 나타

내었다. ON 상태에서는 트랜지스터의 채널을 따라

전류가 흐르게 되므로, 트랜지스터가 큰 입력 전력 에 대해 전류를 안정적으로 통과시키기 위해서는 적 절한 게이트 크기를 가져야 한다. 통과하는 최대 전 력(

max

)에 대한 트랜지스터 최소 게이트 크기 (min

)는 아래 수식을 사용해 구할 수 있다.

max

(1)

min

(2) 식(1)을 통해 전력에 대한 드레인과 소스 사이에 흐르는 전류(

)를 구할 수 있으며, 이를 공정에서 제공하는 단위 게이트(mm)당 트랜지스터의 전류 (drain current)로 나누게 되면 최소 게이트 폭, min

을 구할 수 있다. 이 때

는 회로의 특성 임피던스그림 2. SP2T 스위치의 신호 흐름

Fig. 2. The signal flow of an SP2T switch circuit.

값이다.

min

값을 구한 후 이를 사용할 트랜지스 터의 단일 게이트 폭으로 나누면 게이트 크기를 나 타내는 수치인NGF(Number of Gate Finger) 값을 구 할 수 있다. 작은 전력이 지나가는 수신단의 경우,

min

≃ 의 초기 값을 기준으로 하여 NGF 값을 구하였다.OFF 상태에서는ON 상태의 다른 포트로 지나가 는 전력에 대하여 고려하여야 한다. OFF 상태의 트 랜지스터 드레인 단에ON 상태를 지나가는 전력에 의해 전압(

)이 걸리게 되는데, 이 때OFF 상태의 트랜지스터 동작이

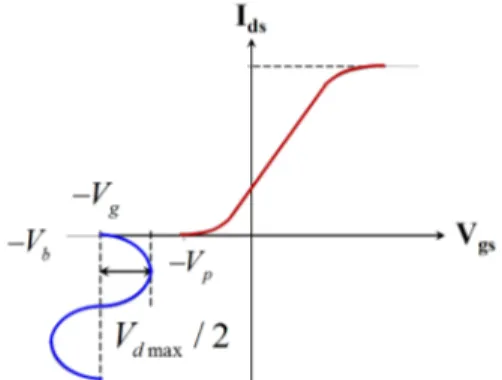

전압에 의해 영향을 받지 않 고OFF 상태를 유지하여야 한다. 큰 전력에도OFF 상태의 트랜지스터가 잘 동작하도록 하기 위해서는 트랜지스터에 걸리는 전압을 이해하여야 한다.그림3에OFF 상태의 트랜지스터에 걸리는 전압 을 나타내었다. 트랜지스터가OFF 상태일 때, 게이 트 바이어스 전압

를 기준으로 드레인 쪽으로 들어오는 드레인 전압

가 스윙하게 된다. 일반적 으로 OFF 상태에서 드레인-게이트, 소스-게이트 임 피던스는 같다고 가정해도 되기 때문에 전압의 절 반인

2가 드레인과 게이트 접지 사이에 걸리게 된다. 먼저 (+) 주기를 고려하면

를 기준으로

2가 스윙할 때 트랜지스터의 핀치 오프 전압 인

를 경계로 넘어서지 않도록 유지하여 OFF 상태의 스위치가ON 상태가 되지 않도록 하여야 한 다. (—) 주기는

를 기준으로

2가 스윙할그림 3. OFF 상태의 트랜지스터에 걸리는 전압 Fig. 3. Voltage swing at an OFF transistor.

때 스위치의 파손을 야기하는 물성적 항복 전압인

를 경계로 넘어서지 않도록 유지하여야 한다. 두 가지 조건의 경계에서 식을 세우면 다음과 같다.

(3)

(4) 이 두 식을 연립하고 정리하여 전압과 전력의 관 계식에 대입하면 다음과 같이 구할 수 있다.

max

(5) 이는 트랜지스터 하나에 대한 입력 전력과 물성 적 전압에 관한 관계식이다.

하나의 트랜지스터로는 큰 입력 전력에 대해서 스위치가OFF 상태를 유지하기 어렵기 때문에 트랜 지스터를 스택(stack)하여 여러 개의 트랜지스터가 큰 전력을 나누어 감당하도록 하였다. 트랜지스터를

series로 연결하여 스택하면 큰 전력에 대한 전압을

트랜지스터 개수

N

만큼 나누기 때문에 큰 전력에도 충분히 정상적으로 동작할 수 있게 된다. 이를 고려 하면 앞의 식 (5)는 다음과 같이 나타낼 수 있다.

max

(6) 이를

N

에 대해서 정리하면 다음과 같이 표현된다.

max

(7)

따라서 시스템 입력 전력

max

가 주어지면 최소 스택 수N

을 구할 수 있다[4]

. 본 논문에서는GSM의 4 W(max) 입력 전력, 50 Ω 특성 임피던스를 기준으 로 설정하였고,

1, 단위 게이트 폭125 μm 를 가지는 트랜지스터를 사용하여NGF와N을 구하 였다.ON 상태의 경우, 삽입 손실과 격리도 특성을 고 려하여 트랜지스터 크기를 결정하게 된다. 삽입 손 실과 격리도의 관계는 트랜지스터의 게이트 크기에 따라 상호적인 특성을 갖게 되므로, 게이트 크기를 적절히 조절하는trade-off 과정을 통하여 삽입 손실 과 격리도 특성이 최상의 조건이 되도록 한다. OFF 상태의 경우 트랜지스터를5개 이상 직렬 연결해야 설계 목표에 맞는 입력 전력에서 충분히 동작할 수 있게 되는데, 일반적인 단일 게이트 트랜지스터를 사용하면 삽입 손실 특성이 많이 악화된다. 따라서 본 논문에서는 멀티 게이트 트랜지스터를 사용하였 다

[5]

. 멀티 게이트 트랜지스터는 스위치 설계용으로 이미 많은 연구가 진행되어 상용 공정에서 제공하고 있다. 멀티 게이트를 사용하게 되면, 스택의 효과를 낼 수 있는 한편 단일 게이트5개를 스택한 것보다 작은 삽입 손실 특성을 얻을 수 있다.본 논문에서는 트리플 게이트와 듀얼 게이트 트 랜지스터를 트랜지스터의 스택을 위해서 사용하였 다. 4 W의 입력 전력을 고려하여 송신단 모두에NGF

=20인series 트랜지스터와NGF=2인shunt 트랜지스 터를 사용하였다. 수신단 저대역은 NGF=8인series 트랜지스터를, 수신단 고대역은NGF=16인series 트 랜지스터와NGF=2인shunt 트랜지스터를 사용하였 다. 마지막으로NGF=20인 트랜지스터를 공통 트랜

지스터(FET A)에 사용하여 수신단에 연결하였다. 송

수신단 모두 트리플 게이트와 듀얼 게이트를 스택하

였고, 송신단shunt 트랜지스터는 송신단이ON 상태

일 때 큰 전력이 지나가므로 마찬가지로 트리플 게 이트와 듀얼 게이트를 스택하였다. 수신단 고대역의

shunt 트랜지스터는 작은 전력이 지나가므로 단일

게이트를 사용하였다. 그림4에 전력 특성을 고려하 여 기본 설계된 스위치를 나타내었다.

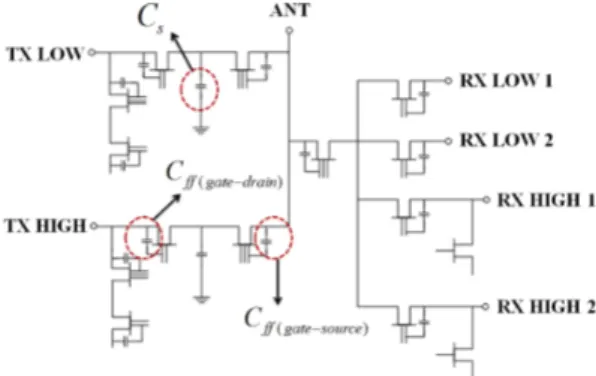

2-3 피드 포워드(Feed Forward)와 Shunt 캐패시터 본 논문에서는 스위치의 전력 및 격리도 특성을

그림 4. 입력 전력을 고려한 SP6T 스위치 설계 회로 Fig. 4. The SP6T switch circuit designed under the in-

put power condition.

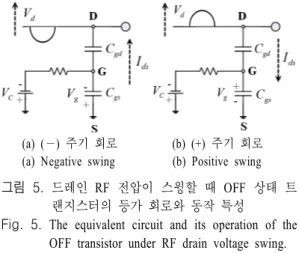

추가 개선시켜 주기 위해 피드 포워드 캐패시터와

shunt 캐패시터를 사용하였다. 피드 포워드 캐패시터

는 전력을 다루는 측면에서 스위치의 동작 특성을 안정적으로 유지할 수 있게 해주며, shunt 캐패시터 는 트랜지스터와 트랜지스터 사이에 사용되어 포트 의 격리도 특성을 개선시켜 주는 역할을 하게 된다. 먼저 피드 포워드 캐패시터의 원리를 알아보기 위해 드레인에RF 전압이 스윙할 때OFF 상태의 트 랜지스터 등가 회로를 그림 5에 나타내었다. 그림 5(a)의

가(—) 주기일 때의 등가 회로를 살펴보면 게이트 전압은 다음과 같이 나타낼 수 있다.

(8) 큰(—) 신호의

가 들어오고

보다 작은 값을 가지게 되면, 그림 5(a)와 같이 소스에서 드레 인 쪽으로 전류가 흐르기 시작하고, 게이트는 접지 보다 낮은 전위이므로 (—)가 된다. 하지만 더 큰 (—) 신호가 드레인에 들어오면 게이트는 상대적으 로 드레인보다 높은 전위를 갖게 되고, 이는 게이트 가 상대적으로 점점(+) 전압을 가지게 만들어FET 가ON 상태가 되어 버리게 된다. 이때, 게이트 전압

는

값에 영향을 받게 된다.그림5(b)는

가(+) 주기일 때의 등가 회로를 나 타낸 그림으로, 동작 원리는 (—) 주기와 비슷하다. 큰(+) 신호의

가 들어오고

가

보다 클 때 전 류는 드레인에서 소스 쪽으로 흐르기 시작한다. 더(a) (—) 주기 회로 (b) (+) 주기 회로 (a) Negative swing (b) Positive swing

그림 5. 드레인 RF 전압이 스윙할 때 OFF 상태 트

랜지스터의 등가 회로와 동작 특성

Fig. 5. The equivalent circuit and its operation of the OFF transistor under RF drain voltage swing.

큰(+) 신호가 드레인에 들어오면 게이트는 상대적 으로 소스보다 높은 전위를 갖게 되고, 이는 게이트 가 점점(+) 전압을 가지게 만들어FET가ON 상태 가 되어 버리게 된다. 이때, 게이트 전압

는 식(8) 에 나타낸 바와 같이 큰

값을 가질 때 소스와의 전압차가 줄어들게 된다.

는(—) 주기 동안에는 큰

, (+) 주기 동안에는 큰

를 가질 경우

와

또는

와

의 전위차는 줄어들게 된다. 따 라서 두 가지 경우 각각 큰

와

값을 만들어 주면 스위치의 전력 특성을 개선시킬 수 있다. 따라 서 드레인-게이트와 소스-게이트에 병렬로 피드 포 워드 캐패시터(

)를 달아주면 더 큰

와

값 을 만들어주는 효과를 가지게 되어 전력 특성을 개 선시킬 수 있다[6],[7]

.Shunt 캐패시터(

)는 직렬로 연결된 트랜지스터 사이에 위치하여 그림 6과 같이 트랜지스터가 OFF 상태일 때 큰 전력의 신호가 넘어 들어오는 것을 접그림 6. 격리도 개선을 위해 shunt 캐패시터가 포함

된 경로의 회로

Fig. 6. The switch circuit with a shunt capacitor for isolation improvement.

지로 빼서 격리도 특성을 개선시켜 주는 역할을 할 수 있다. 따라서 휴대 단말기용ASM을 위한 스위치

회로에 shunt 캐패시터 기법을 시도하여 보았다.

Shunt 캐패시터가 스위치 특성에 어떤 영향을 주

는지 알아보기 위해서 트랜지스터의ON 상태 저항 을

R

ON, OFF 상태 캐패시터를C

OFF라 하면 포트2 경 로의ON, OFF 상태에 대한

을 다음과 같이 구할 수 있다.

(9)

(10) 식에 나타난 바와 같이

이 작아짐에 따라

의 크기가 커져 삽입 손실이 작아지는 것을 알 수 있으며, 이는 큰 트랜지스터를 사용하여

의 값을 줄였을 때 삽입 손실이 작아지는 결과를 설명 할 수 있다.

값이 커지게 되면

의 크기가 작 아져 삽입 손실이 증가하는 것을 알 수 있다. 또한,

값이 커짐에 따라

의 크기가 커짐을 알 수 있고 큰FET를 사용하여

값을 키웠을 때, 격 리도 특성이 나빠지는 결과를 설명할 수 있다.

값이 커지게 되면

크기가 작아져 삽입 손실 이 증가하지만 격리도 특성이 좋아지는 것을 알 수 있다[8]

.따라서 적절한

의 선택은 삽입 손실과 격리도 의 특성을 개선하는데 있어 중요하게 된다. 피드 포 워드 캐패시터와 shunt 캐패시터가 적용된 스위치 회로를 그림7에 나타내었다. 피드 포워드 캐패시터 는 소자의 전력 능력을 향상시키기 위해 사용되므로 입력 전력에 따른 삽입 손실 및 격리도 특성 변화가 스위치에 요구된 최대 입력 전력에서 관찰되지 않을 때까지 값을 증가시켜 사용하였다.

는 삽입 손실 의 변화가 성능 목표의 범주를 벗어나지 않는 범위 내에서 격리도를 증가시킬 수 있는 값으로 정해지며

값에 따른 삽입 손실과 격리도 변화 추이를 그래 프로 확인한 후 선택되었다. 본 논문에서는 피드 포 워드 캐패시터 값으로 3.26 pF을 사용하였고 shunt 캐패시터는 스위치 특성을 고려하여 0.34 pF 값을그림 7.

와

가 적용된 SP6T 스위치 Fig. 7. The SP6T switch circuit with

and

.사용하였다.

2-4 Shunt 트랜지스터의 기생 인덕턴스 효과 Series-shunt 스위치 구조에서series 트랜지스터가 OFF 상태일 때, shunt 트랜지스터는 ON 상태가 된 다. 이때shunt 트랜지스터는 그림8(a)과 같은 등가 회로를 가지며, 비아 홀(via hole) 공정을 사용하지 않

는pHEMT 스위치 공정의 특성상 본딩 와이어에 의

한 기생 인덕턴스 성분

가 발생하게 된다. 주파수 가 올라갈수록

의 영향이 커져 스위치의 격리도 특성을 악화시키게 되므로

의 영향을 상쇄시켜 주기 위해서 그림8(b)와 같이

에 직렬로

를 달 아 공진 효과를 활용함으로써 격리도 특성을 개선시 킬 수 있다[9]

. 이러한 공진 기법을 스위치 회로에 적 용하여 격리도 특성 개선을 시도하였고, 시뮬레이션 을 통해

값을 결정하였다. 본 논문에서는1 mil

(a) (b)

그림 8. Shunt 트랜지스터 ON 상태 등가 회로(a)와

C

p를 활용한 기생 인덕턴스의 제거(b)Fig. 8. The equivalent circuit(a) of an ON-state shunt transistor and elimination(b) of its parasitic in- ductance effect using Cp.

그림 9. DC 바이어스 인가를 위한 회로도 Fig. 9. The schematic circuit for DC biasing.

직경, 30 mils 길이의Au 본딩 와이어를 사용하는 기 준으로

를 구하였고, 47 pF의SMD(Surface Mount Device) 소자를 사용하였다.2-5 DC 바이어스

스위치 회로에 대한 바이어스 회로는 게이트에3 V의 전압이 인가될 때ON 상태를 유지하고0 V의 전압을 인가할 때OFF 상태를 유지할 수 있도록 설 계되었다. 이는 피드 포워드 저항을 통해 드레인과 소오스에 공통적으로 3 V의 전압이 인가된 상태에 서 게이트에3 V 또는0 V의 전압을 부여함으로써 ON, OFF 동작을 수행하게 되는 것이다. DC 바이어 스 저항과 피드 포워드 저항은15 kΩ을 사용하였으 며, DC 차단용 캐패시터는100 pF의SMD 소자를 사 용하였다. 격리도 특성 개선을 위해 삽입한

C

p또한, DC를 차단하는 역할을 하여 드레인과 소오스를 동 일 전압으로 유지시켜 주게 된다.Ⅲ. 시뮬레이션 및 레이아웃

저손실 및 고전력 특성의GSM/EGSM/DCS/PCS 4 중 대역용SP6T RF 스위치는shunt 캐패시터를 사용 하지 않은 경우(

미부착)와 사용한 경우(

부착) 두 가지 형태로 설계되었다. 상용 제품을 기준으로 설계 목표를 설정하였고, 표 1에 이를 나타내었다[10],[11]

. RX의 경우 신호를 수신하는 수동적인 동작을수행하므로RX 단자 상호간의 격리도는 별도로 요

표 1. SP6T 스위치 설계 목표

Table 1. Design specifications of the SP6T switch.

Insertion loss [dB]

TX low(GSM/EGSM) 0.4 TX high(DCS/PCS) 0.5 RX low(GSM/EGSM) 0.8 RX high(DCS/PCS) 1.0

Isolation [dB]

TX-TX low(GSM/EGSM) 25 TX-TX high(DCS/PCS) 20 TX-RX low(GSM/EGSM) 35 TX-RX high(DCS/PCS) 30 2nd Harmonic

[dBc]

4 W TX input(GSM/EGSM) 2 W TX input(DCS/PCS) 70 3rd Harmonic

[dBc]

4 W TX input(GSM/EGSM) 2 W TX input(DCS/PCS) 70

구되지 않아 설계 목표에서 제외되었다.

대만의WIN Semiconductors사의WIN PD50-01 0.5

μm pHEMT 라이브러리 모델을 사용하여 Agilent

ADS 시뮬레이션을 진행하였다

[12],[13]

. 라이브러리는 스위치 설계용으로 싱글 게이트, 듀얼 게이트, 트리 플 게이트 트랜지스터의 소신호 모델만 제공하며, 대신호 모델은 제공되지 않아 큰 전력에 대해서는 직접적인 시뮬레이션을 수행할 수 없었으나 제공된 단위소자에 대한 특성으로부터 대신호 특성을 간접 적으로 추정하였다. NGF 값과 ON, OFF 상태를 설 정하면 각각의 상태에 대해 계산된S

파라미터 값을 활용하여 시뮬레이션을 수행하였다. 칩의 패드, 본딩와이어, DC 블록용 캐패시터와 같은 기생 요소의

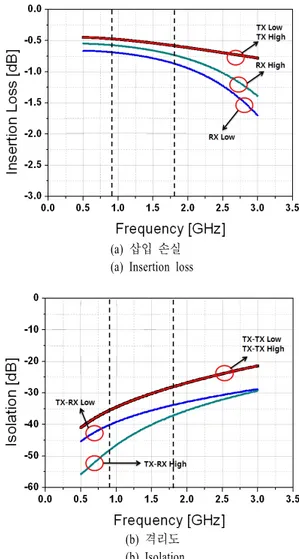

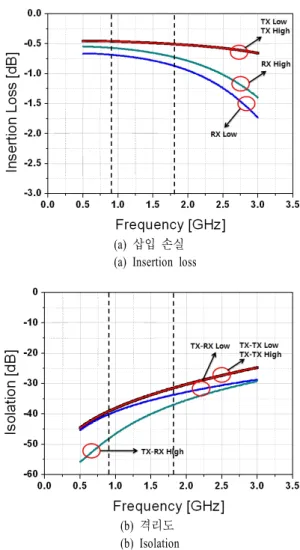

영향을 고려하여 시뮬레이션을 하였으며, DC 블록 용 캐패시터의 값은100 pF를 사용하였다. 시뮬레이 션된 설계 결과를 그림10와11에 그래프로 나타내 었으며, 이를 표 2에 요약, 정리하였다.

시뮬레이션을 수행한 결과, 설계 목표에 거의 만 족하는 결과를 얻을 수 있었고

미부착 샘플과

부착 샘플을 비교할 때 삽입 손실이 오차 범위 내에서 거의 유사한 결과를 보여 shunt 캐패시터가 삽입 손실의 열화를 최대한 억제하면서 격리도 특성 을 개선시키는 역할을 함을 알 수 있었다. 반사 손실 의 경우0.5~2.5 GHz 영역에서 25 dB 이하의 성능 이 확보될 수 있도록 설계되었다.(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 10.

미부착 샘플의 스위치 칩 설계 결과 Fig. 10. Simulated results of the sample without

.표 2. SP6T 스위치 칩 시뮬레이션 결과 요약 Table 2. The summary of the simulated results of SP-

6T switches.

Insertion loss [dB]

TX low

TX high

RX low

RX high

미부착 0.47 0.60 0.69 0.76

부착 0.46 0.52 0.69 0.75Isolation [dB]

TX-TX low

TX-TX high

TX-RX low

TX-RX high

미부착 35.6 27.5 40.2 36.6

부착 39.2 31.0 40.2 36.2(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 11.

부착 샘플의 스위치 칩 설계 결과 Fig. 11. Simulated results of the sample with

.설계된 스위치 회로를 제작하기 위해 레이아웃을 수행하였다. 먼저 패드와 트랜지스터를 배치하고 저 항, 캐패시터를 배치하여 금속선으로 결선하는 방식 으로 이루어졌다. 금속선의 연결에 의한 영향을 최 소화하기 위해1차 금속(Met 1)과2차 금속(Met 2)을 비아를 통해 연결하여 금속선을 두껍게 만들어 결선 하였고, 금속선 길이에 의한 손실을 줄이기 위해 소 자 사이의 간격을 최소화하고, 금속선의 폭은 넓게, 길이는 짧게 레이아웃하였다. 또, 와이어 본딩에 의 한 기생 인덕턴스의 영향을 최소화하기 위해서 본딩 을 최대한 많이 할 수 있도록 RF 신호가 지나가는 패드의 크기를 크게 하였다.

미부착 샘플과

부착 샘플의 차이는 shunt 캐패시터의 존재 유무이그림 12. SP6T 스위치 칩의 레이아웃 Fig. 12. The SP6T switch chip layout.

므로 모든 레이아웃은 동일하다. 따라서

부착 샘 플의 레이아웃만 그림12에 나타내었다. 그림에 표기한 shunt 캐패시터만을 제거하면

미부착 샘플의 레이아웃과 같다. 그림12에 설계된 스위치 칩의 레이아웃 크기는 1.2×1.5 mm

2

이다.Ⅳ. 측 정

WIN Semiconductors사의 파운드리 공정을 이용하 여 칩을 제작하였으며, 제작된 칩의 사진을 그림13 에 나타내었다.

제작된 칩의 측정을 위해서 시험용 PCB 보드에 에폭시를 사용하여 칩을 붙이고 와이어 본딩으로 칩 의 패드와 시험용 보드를 연결하였다. 시험용 보드 에 의한 손실을 제거하기 위하여 시험용 보드에 사 용된 신호선 부분만을 따로 제작하여 스위치 측정

(a)

미부착 샘플 (b)

부착 샘플 (a) Sample without

(b) Sample with

그림 13. 제작된 SP6T 스위치 칩의 사진Fig. 13. The microphotographs of the fabricated SP6T switch chips.

결과를 디임베딩(de-embedding) 하였다. 측정은

S

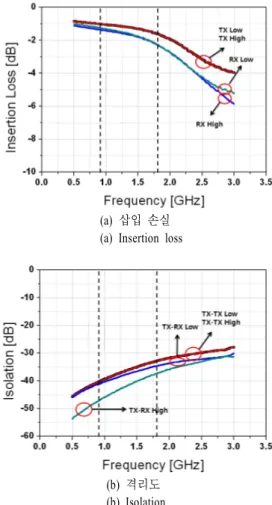

파 라미터 측정과 입력 전력에 따른 스위치의 전력 특 성 측정으로 나누어 진행되었다.4-1 S 파라미터 측정

Agilent사의 회로망 분석기인E8358A를 이용하여

각 샘플을 측정하였다. 측정 결과 그래프를 그림14 과15에 나타내었고, 디임베딩한 결과를 표3에 정리 하였다.

측정 결과를 시뮬레이션과 비교했을 때 삽입 손 실과 격리도 특성에서 거의 비슷한 결과를 얻을 수

(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 14.

미부착 샘플의 S 파라미터 측정 결과 (보정 전)Fig. 14. The measured S parameter results of the sam- ple without

(before de-embedding).(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 15.

부착 샘플의 S 파라미터 결과(보정 전) Fig. 15. The measured S parameter results of the sam-ple with

(before de-embedding).있었다. 하지만DCS/PCS 대역의RX 삽입 손실의 경 우 비록 설계 목표보다는0.2 dB의 증가만 있었지만, 설계에서 예상된 결과보다 손실이 샘플의 종류에 따 라0.45~0.68 dB 더 발생하였다. 이는 설계 시 소자 사이 결선에 들어간 금속선을 완벽하게 고려하지 못 한 것과 조립에서 수반되는 칩과 시험용 보드 사이 의 본딩 와이어 효과가 높은 주파수에서 임피던스 부정합 효과를 더 크게 발생하는 것에서 원인을 찾 을 수 있다.

또한, WIN Semiconductors사의 공정을 이용해SP- 6T 스위치 칩을 설계한 참고문헌 [3]에서도 PCS/

DCS와 같은 높은 주파수 영역에서 삽입 손실의 특 성 열화가 발생된 것으로 보아 파운드리에서 제공하 는 모델이 예측하는 것과 달리 실제 소자의 특성은

표 3. SP6T 스위치 칩의 S 파라미터 측정 결과 요 약(보정 후)

Table 3. The summary of the measured results of the fabricated SP6T switch chips(after de-embe- dding).

Insertion loss [dB]

TX low

TX high

RX low

RX high

미부착 0.50 0.57 0.83 1.20

부착 0.52 0.72 0.86 1.43Isolation [dB]

TX-TX low

TX-TX high

TX-RX low

TX-RX high

미부착 36.5 28.3 40.9 35.9

부착 40.5 32.3 41.2 36.62 GHz 근처에서 충분한 스위치 특성을 제공하지 못

하는 것으로 판단된다.

반사 손실의 경우 전체적으로20 dB 이하의 특성 이 측정되었으나, 시험용 보드 자체의 반사 손실 특 성으로 인해1.5~2.0 GHz에서는15~20 dB의 반사 손실이 측정되었다.

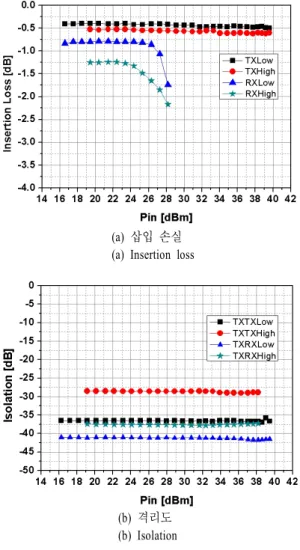

4-2 전력 특성 측정

제작된 SP6T 스위치 칩이 4 W(GSM/EGSM)와2

W(DCS/PCS)의 입력 전력에도 안정적으로 동작하여

야 하므로 시스템 최대 요구 전력까지 입력 전력을 변화시킬 때

S

파라미터 측정 결과와 비슷한 삽입 손실 및 격리도 특성을 보여야 한다. 또한, 큰 입력 전력이 한 쪽 경로로 지나갈 때 나머지 경로들은 OFF 상태를 유지하고 입력 신호에 대해서2차, 3차 고조파도 충분히 억제시켜 줄 수 있어야 스위치가 파손되거나, OFF 상태를 유지하지 못하고ON 상태 가 되어 오동작하는 일이 발생하지 않게 되며, 고조 파에 의해 신호 성분이 왜곡되어 나타나지 않게 된 다. 따라서 전력 특성 측정은 크게 두 가지 단계로 나뉜다. 먼저 앞에서 측정한 삽입 손실과 격리도 특 성을 측정하여 안정적으로 동작하는지 확인 후2차, 3차 고조파 특성을 측정하게 된다. 전력 특성 측정 을 위한 장비와 부품의 셋업 및 모델을 그림16의 블 록도에 나타내었다.증폭기는 원하는 입력 전력을 만들어 주기 위해

(a) 삽입 손실과 격리도 특성 측정 셋업 (a) Test set-up for insertion loss and isolation

(b) 2차 및 3차 고조파 억제 특성 측정 셋업 (b) Test set-up for 2nd/3rd harmonics suppression 그림 16. 전력 특성 측정 셋업

Fig. 16. Power test set-up.

서 사용되었으며, 아이솔레이터는 반사파를 흡수하 여 증폭기를 보호하는 용도로 사용되었다. 커플러와 파워미터는 DUT(Device Under Test)인 스위치에 들 어가는 전력을 측정하기 위해 사용하였다. 마지막으 로 스위치에서 나오는 전력을 스펙트럼 분석기로 확 인하여 두 전력의 차이를 측정함으로써 스위치의 손 실을 측정하였다. 고조파 측정에서 사용된 대부분의 장비 및 부품은 같은 모델이며, 대역 통과 여파기는 입력 신호에 대해 증폭기가 만들어내는 고조파를 충 분히 제거하기 위해서 대역외 감쇄 특성이 70 dBc 이상인 제품을 사용하였다. 먼저 삽입 손실 및 격리 도의 전력 특성 측정 결과를 그림17과18에 나타내 었다.

미부착 샘플의 삽입 손실 측정 결과, 송신단은 큰 전력에도 충분히 안정적으로 동작함을 알 수 있 었고, 수신단의 경우 시스템에서 작은 전력을 요구 하므로 작은 전력에서 충분히 안정적으로 동작하였 고, 큰 전력에서는 손실이 점점 악화되는 것을 확인 할 수 있었다. 격리도는 큰 전력의 입력에서도OFF 상태를 잘 유지하여 안정적으로 동작함을 알 수 있(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 17.

미부착 샘플의 전력 특성 측정 결과 Fig. 17. The power measurement of the sample with-out

.다.

부착 샘플의 경우 삽입 손실과 격리도 모두 GSM/EGSM 대역에서는4 W, DCS/PCS 대역에서는2 W 이상의 전력에서 안정적으로 동작함을 알 수

있었다.

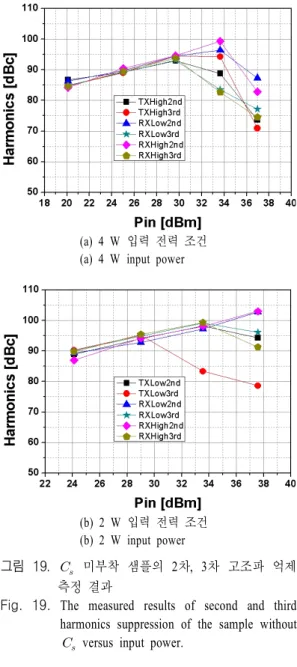

고조파 특성은2차, 3차 고조파를 측정하게 되는 데, 마찬가지로GSM/EGSM TX 대역에서4 W, DCS/

PCS TX 대역에서 2 W의 입력 신호를 기준 신호로

설정하고, TX Low, TX High, RX Low, RX High 포트 의2차, 3차 고조파를 측정하여 기준 신호와의 차이 를 구함으로써2차, 3차 고조파 억제 특성을 측정하 게 된다. 고조파 특성 측정 결과를 그림 19과20에 각각 나타내었다.

(a) 삽입 손실 (a) Insertion loss

(b) 격리도 (b) Isolation

그림 18.

부착 샘플의 전력 특성 측정 결과 Fig. 18. The power measurement of the sample with

.고조파 억제 특성을 측정한 결과, 4중 대역인GSM

/EGSM/DCS/PCS의 모든TX 신호에 대해 설계 목표

로 했던70 dBc보다 더 좋은75 dBc 이상의2차, 3차 고조파 억제 특성을 얻을 수 있었다. 2차, 3차 고조 파 억제 특성을 포함한 스위치 회로의 전체 특성을 동일 전력 조건(33 dBm, 35 dBm)에서 기존 논문들 의 결과와 비교하여 표4에 나타내었다

[4],[14]

.Ⅴ. 결 론

본 논문에서는 유럽형 GSM/EGSM/DCS/PCS의4 중 대역에서 저손실, 고전력 특성을 갖는SP6T 스위

(a) 4 W 입력 전력 조건 (a) 4 W input power

(b) 2 W 입력 전력 조건 (b) 2 W input power

그림 19.

미부착 샘플의 2차, 3차 고조파 억제 측정 결과Fig. 19. The measured results of second and third harmonics suppression of the sample without

versus input power.치를 설계하였고, WIN Semiconductors사의 0.5 μm pHEMT 공정을 이용하여 제작하였다. 먼저series와

series-shunt 구조를 혼용하여 스위치 특성을 위한 최

적의 구조를 선택하였고, 칩 크기를 줄이기 위해 수 신단에 공통 트랜지스터를 적용하였다. 또한, 시스 템에 사용되는 입력 전력을 고려하여 ON, OFF 각 각의 상태에 대해 트랜지스터의 게이트 크기와 스 택 수를 결정하여 스위치를 설계하였다. 마지막으로 스위치 특성 개선을 위하여 피드 포워드 캐패시터, shunt 캐패시터, shunt 트랜지스터의 기생 인덕턴스 공진 기법을 사용하였다. 제작된 스위치는 1.2×1.5

(a) 4 W 입력 전력 조건 (a) 4 W input power

(b) 2 W 입력 전력 조건 (b) 2 W input power

그림 20.

부착 샘플의 2차, 3차 고조파 억제 측 정 결과Fig. 20. The measured results of second and third harmonics suppression of the sample with

versus input power.mm

2

의 크기를 가지며, S 파라미터 특성과 전력 특성 이 평가되었다. 스위치 측정 결과, DCS/PCS 대역의 삽입 손실을 제외한 모든 성능이 설계 규격과 비교 해 만족되었으며, 우수한 격리도 특성을 확보하였 다. 또한, 전력 특성 측정 결과, 최대 입력 전력4 W 이상의 전력에도 충분히 안정적으로 동작하였으며, 2차 및3차 고조파 억제 특성도75 dBc 이상으로 모 두 설계 목표를 충족하였다. 개발된SP6T 스위치 칩 은 고대역의RX 삽입 손실을 일부 개선할 경우 현재 상용 휴대폰에 직접 적용 가능한 수준이며, SP9T 개 발에 적극 활용될 수 있다.표 4. SP6T 스위치 측정 결과 비교

Table 4. Comparison of the measured results of the SP6T switches.

Parameter Specification This work

Ref.

[4]

Ref.

[14]

Insertion loss [dB]

TX Low 0.50 0.3 0.7 TX High 0.57 0.45 0.7 RX Low 0.83 0.7 0.8 RX High 1.20 0.9 0.8

Isolation [dB]

TX-TX Low 36.5 28 - TX-TX High 28.3 22 - TX-RX Low 40.9 33 40 TX-RX High 35.9 27 30 2nd

Harmonic [dBc]

35 dBm TX input 82 80 73 33 dBm TX input 85 80 74 3rd

Harmonic [dBc]

35 dBm TX input 79 80 76 33 dBm TX input 86 75 71

참 고 문 헌

[1] D. Kelly, C. Brindle, C. Kemerling, and M. Stuber,

"The state-of-the-art of silicon-on-sapphire CMOS RF switches", 2005 Compound Semiconductor Inte-

grated Circuit Symposium Digest, pp. 200-202, Oct.

2005.

[2] D. Gotch, T. Goh, and R. Jackson, "State-of-the-art low loss, high isolation SP6T switch for handset applications", European Conference on Wireless Te-

chnology, pp. 17-20, 2004.

[3] J. Wu, S. Chen, C. Huang, C. Tang, J. Li, and C.

Tsai, "pHEMT SP6T ICs for quadband GSM hand- set applications", Asia-Pacific Microwave Conferen-

ce, pp. 1-4, Dec. 2007.

[4] D. Prikhodko, Y. Tkachenko, S. Sprinkle, R. Carter, S. Nabokin, and J. Chiesa, "Design of a low VS- WR harmonics, low loss SP6T switch for GSM/

Edge applications", in Proc. 2nd European Micro-

wave Integrated Circuits Conference, pp. 32-35,

Oct. 2007.[5] K. Numata, Y. Takahashi, T. Maeda, and H. Hida,

"A +2.4/0 V controlled high power GaAs SPDT antenna switch IC for GSM application", IEEE RF-

IC Symposium, pp. 141-144, 2002.

[6] K. Chang, I. Baul, and V. Nair, RF and Microwave

Circuit and Component Design for Wireless Sys- tems, John Wiley & Sons, 2002.

[7] Yibing Zhao, Shuyun Zhang, and Robert J. Mc- Morrow, "High power, high linearity and low inser- tion loss single pole double throw transmitter/re- ceiver", US Patent 7098755, Aug. 2006.

[8] K. Kawakyu, Y. Ikeda, M. Naaoka, K. Ishida, A.

Kameyama, T. Nitta, M. Yoshimura, Y. Kitaura, and N. Uchitomi, "A novel resonant-type GaAs SPDT switch IC with low distortion characteristics for 1.9 GHz personal handy-phone system", International

Microwave Symposium Digest, pp. 249-252, Jun.

1996.

[9] K. Nakahara, K. Miyaguchi, M. Hieda, H. Kurusu, Y. Iyama, and T. Takagi, "Switches with capacitor cancelled parasitic inductance of FET", Interna-

tional Microwave Symposium Digest, pp. 647-650,

2001.[10] http://www.rfmd.com [11] http://www.triquint.com

[12] Advanced Design System 2008, Agilent.

[13] http://www.winfoundry.com

[14] C. Tinella, O. Richard, A. Cathelin, F. Reaute, S.

Majcherczak, F. Blanchet, and D. Belot, "0.13 μm CMOS SOI SP6T antenna switch for multi-stan- dard handset", 2006 Topical Meeting on Silicon

Monolithic Integrated Circuits in RF Systems, pp.

58-61, 2006.

권 태 민

2009년 2월: 충남대학교 전기정보 통신공학부(공학사)

2011년 2월: 충남대학교 전자전파 정보통신공학과(공학석사) 2011년 1월~현재: LG전자 MC사업

부 연구원

[주 관심분야] 초고속 및 초고주파 집적회로, 마이크로파 회로

박 용 민

2009년 2월: 동아대학교 전자공학 과(공학사)

2010년 3월~현재: 충남대학교 전자 전파정보통신공학과 석사과정 [주 관심분야] 마이크로파 회로 및

소형 레이더 모듈

김 동 욱

1996년 8월: 한국과학기술원 전기 및 전자공학과 (공학박사) 1991년 8월~2000년 5월: LG종합

기술원 선임연구원

2000년 6월~2002년 8월: 텔레포스 (주) 연구소장

2002년 9월~2004년 9월: 에스원기 술연구소 응용기술팀장

2009년 6월~2009년 12월: 전자통신연구원 초빙연구원 2010년 1월~2011년 1월: UCSD 방문연구원

2004년 10월~현재: 충남대학교 전파공학과 교수 [주 관심분야] 초고속 및 초고주파 집적회로, 마이크로파

및 밀리미터파 전력 모듈 및 초소형 레이더 모듈