12

웨어러블 디바이스를 위한 다중 센서/통신용 모듈형 플랫폼 기술 Modular platform techniques for multi-sensor/communication of

wearable devices

박 성 훈

*

, 김 주 언**

, 윤 동 현**

, 백 광 현** ★

Sung Hoon Park

*

, Ju Eon Kim**

, Dong-Hyun Yoon**

, Kwang-Hyun Baek** ★

Abstract

In this paper, a modular platform for wearable devices is proposed which can be easily assembled by exchanging functions according to various field and environment conditions. The proposed modular platform consists of a 32-bit RISC CPU, a 32-bit symmetric multi-core processor, and a 16-bit DSP. It also includes a plug & play features which can quickly respond to various environments. The sensing and communication modules are connected in the form of a chain. This work is implemented in a standard 130 nm CMOS technology and the proposed modular wearable platforms are verified with temperature and humidity sensors.

요 약

본 논문에서는 다양한 분야와 환경에서 필요에 따라 기능을 쉽게 교환하고 조립이 가능한 모듈형 웨어러블 플랫 폼을 제안한다. 제안된 플랫폼은 국내 CPU 코어 기반의 모듈형 플랫폼과 다양한 환경에 빠르게 대응하여 자유롭게 연결 가능한 plug & play 플랫폼으로 구성된다. 설계된 SoC는 32-bit RISC CPU, 32-bit symmetric multi-core processor, 그리고 16-bit DSP (CDSP)로 구성되고 여기에 필요에 따라 센서 모듈과 통신 모듈이 체인 형태로 연결 된다. SoC 칩은 130nm 공정으로 개발되었고 온도와 습도 센서를 이용하여 제안된 모듈형 웨어러블 플랫폼의 기능 의 동작을 검증하였다.

Key words : wearable devices, modular platform, SoC, multi core, sensor

* Zaram Technology, Inc., Gyeonggi-do, Korea

** School of Electrical and Electronics Engineering, Chung-Ang University, Seoul, Korea

★ Corresponding author

e-mail : kbaek@cau.ac.kr tel : 02-820-5765

※ Acknowledgment

This research was supported by Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education(No. 2015R1D1A1A01060031) and this research was supported by the MSIT(Ministry of Science and ICT), Korea, under the ITRC(Information Technology Research Center) support program(IITP-2016-0-00309-002) supervised by the IITP(Institute for Information & communications Technology Promotion)

Manuscript received Sep. 21, 2017; revised Sep. 26, 2017 ; accepted Sep. 26, 2017

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License

(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in

any medium, provided the original work is properly cited.

Ⅰ. 서론

최근 소형화, 경량화, 신뢰성 확보가 가능한 웨 어러블 디바이스 분야의 요소기술과 ICT 플랫폼 기술에 대한 연구가 활발하다. 의류 및 기구에 센 서, 플랫폼, 카메라 등 다양한 입출력장치를 통해 환경정보를 수집함으로써 신체 착용을 용이하게 할 뿐만 아니라 다양한 정보를 실시간으로 제공 하는 것이 가능해졌다. 하지만 현재 연구 중인 웨 어러블 디바이스 기술들은 빠르게 변화하는 산업 의 다양한 분야별, 환경별 전문적인 대응에 한계 를 가진다. 또한 의류형태의 웨어러블 디바이스는 고가격일 뿐만 아니라 개별 환경에 맞는 소량, 다 제품의 개발에 어려움이 있다. 따라서 필요에 따 라 기능을 쉽게 교환, 조립할 수 있는 표준형 모 델의 모듈형 웨어러블 플랫폼이 요구 되며 이는 지속적으로 변화하는 다양한 환경에 빠르게 대응 하는 동시에 수리·교환·생산이 용이한 장점이 있 다. 본 논문에서는 국산 코어기반의 모듈형 플랫 폼과 자유롭게 연결 가능한 다수의 센서, 통신, 카메라 등의 모듈, 연동 plug & play 플랫폼을 제 안 한다.

Ⅱ. 본론 1. CPU 코어 및 SoC 구성

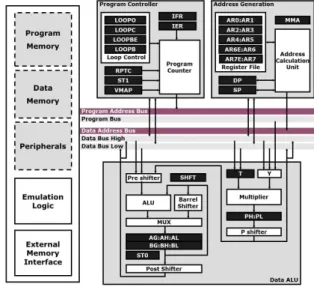

설계한 SoC의 전체 블록도는 그림 1. 과 같다.

Fig. 1. Block diagram of SoC 그림 1. SoC 블록도

설계된 SoC는 32-bit RISC CPU (MENSA), 32-bit Symmetric Multi-core processor (SPARC V8), 그리고 16-bit DSP 2 array (2개의 16-bit CDSP16)으로 구성 [1-3] 되어 있고 각각의 CPU 는 모두 최대 100MHz까지 동작 가능하다. 특히 32-bit RISC CPU들은 리눅스 OS를 지원하기 위 해서 cache뿐만 아니라 MMU(TLB)를 지원하도 록 구성하였다. MENSA CPU와 SPARC V8 CPU는 동시에 사용할 수 없기 때문에 추가적인 핀을 이용하여 사용할 CPU를 결정하고 선택되지 않은 CPU에는 클럭을 제공하지 않음으로써 전력 소모를 감소하였다. 각 CPU의 프로그램 개발을 위해서 각각의 디버거 인터페이스를 지원한다.

가. 32-bit SPARC V8 CPU

그림 2. 는 SoC에 적용된 32-bit SPARC CPU 의 블록도이다. SPARC V8 CPU는 MENSA CPU에 비해 면적이 작은 장점이 있다. 저전력 SoC를 설계하기에 유리하고, 최종적으로 생산될 경우 비용면에서도 저렴하다. 설계된 SPARC V8 은 FPU(floating point unit)을 제외하여 트랜지스 터의 개수를 감소시켰다. 표 1. 은 SPARC V8 프 로세서의 구성을 보여준다.

Fig. 2. Block diagram of 32-bit SPARC V8 CPU 그림 2. 32-bit SPARC V8 CPU 블록도 Table 1. Processor configuration of SPARC V8 표 1. SPARC V8 프로세서 구성

Data cache 8K-byte, 2-way (line size 8) Instruction cache 8K-byte, 2-way (line size 8)

FPU N/A

Register file 8 general register, 8 x 16 register MMU 32 instruction TLB, 32 data TLB H/W MUL/DIV Hardware multiplier and divider

DSU (debug support unit)

Blocks Function PLL0 ~ 2 CPU, USB, Audio clocks 32KB on-chip

SRAM

SRAM for module with small memory

256M-bit

SDRAM Main memory of RISC CPU Serial flash

interface

Save boot program and data RISC CPU

USB1.1 controller Maximum 12M bps communication Ethernet interface 100Mbps ethernet interface I2C/I2S

interfaces Interface for I2C and IS2 Camera &

Display interface

Support small camera and LCD display

GPIO 16-bit GPIO

SD card interface Maximum 50MHz communication Timer support five timer, three PWM

RTC Use 32.768KHz clock

COM Communication block for plug & play module

나. CDSP16 CPU

설계된 SoC는 아날로그 센서 신호를 처리해야 할 경우를 대비하여 일반적으로 사용되는 CDSP16을 내장 하였다. 그림 3. 은 CDSP16의 블 록 도를 보여준다. 아날로그 센서 신호가 ADC를 거쳐서 메모리에 저장되면 CDSP16은 이것을 분 석하여 그 결과를 CPU에 전달한다. CDSP16은 단순한 신호처리만 반복적으로 수행하기 때문에 instruction/data memory가 최소한으로 설계되었 다. CPU를 이용해서 DSP의 역할을 수행할 수도 있지만 디지털신호처리의 경우 DSP가 효율적이 다. 표 2. 는 CDSP16 프로세서의 구성을 보여 준다.

Fig. 3. Block diagram of CDSP16 그림 3. CDSP16 의 블록도

Table 2. Processor configuration of CDSP16 표 2. CDSP16 프로세서 구성

Data RAM 4KB

Program RAM 4KB

Overlay RAM 2KB

8-address register AR0 ~ AR7

2-acc register A, B

1-multiply register P

Hardware loop and single instruction repeat DSP indirect addressing mode Hardware multiply and accumulation

다. 그 외 블록들

표 3. 에서는 SoC의 다른 블록들은 보여 준다.

Table 3. The other blocks 표 3. 그 외의 블록들

2. 통신/센서 모듈 인터페이스

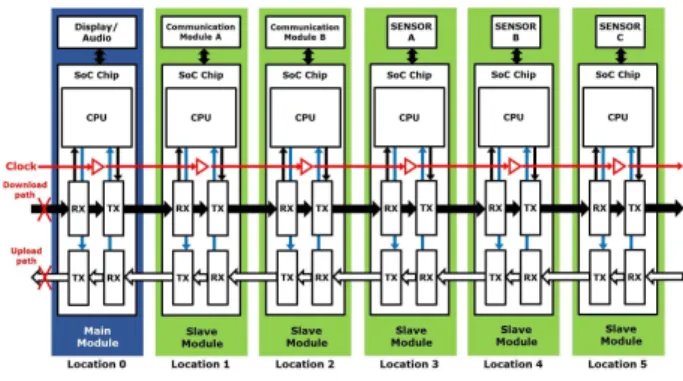

Fig. 4. The connection of sensor and communication modules

그림 4. 센서 모듈과 통신 모듈의 연결 방법

웨어러블 디바이스를 위한 다중 센서/통신용 모

듈형 플랫폼을 구현하기 위해 모듈화된 SoC가

plug & play 형태로 상호간의 인터페이스를 하며

필요 따라 통신/센서 모듈로서 역할을 한다. 그림

4. 는 체인 형태로 연결 된 모듈을 보여 준다. 각

모듈을 체인으로 연결하기 위해 COM 블록이 설계

되었다. COM 블록은 메인 모듈과 슬레이브 모듈

Header Function

LOC

Location. Indicate the destination of transferred Data. If LOC is 0, the destination is main module. If LOC is not 0, that is slave module

TYPE

Use to indicate the type of transferred Data or location of that. If LOC is 0xFF and TYPE is 0xFF, there is command for indicating the location of Data. If location indicator is transferred, the location of slave is saved at Data and then Data is incremented by 1 and transferred to next slave. The location indicator is used for plug & play function. Other TYPEs are not fixed in hardware, but are fixed in software.

Length

Indicate the length of Data (0 ~ 512). If packet length is longer than 512, latency problem occur during communication.

The value of Length is should be exact to check the followed Data and FCS.

BCH code BCH code for 2-bit error correction.

PARITY Even parity. 6-byte header is set to be even parity.

로 이루어진 2개의 체인을 구성할 수 있다. 2개 의 체인 중 한 개는 데이터양이 상대적으로 많은 통신 모듈들을 연결하고, 나머지 한 개의 체인에 는 데이터양이 적은 센서 모듈들을 연결 한다. 이 로 인해 센서 체인 clock 주파수를 낮게 설정할 수 있게 되고 전력소비를 최적화 할 수 있다.

가. 모듈 간 통신 구성

모듈 간 통신을 위해 COM블록은 다운로드 통 신을 위한 TX, RX블록과 업로드를 위한 TX, RX 블록으로 구성된다. 통신 속도를 높이기 위해 clock에 동기된 시리얼 방식을 사용하였으며 통신 속도는 메인 모듈이 결정하고, 체인에 연결된 모 든 슬레이브 모듈은 동일한 클럭을 이용하여 통 신한다.

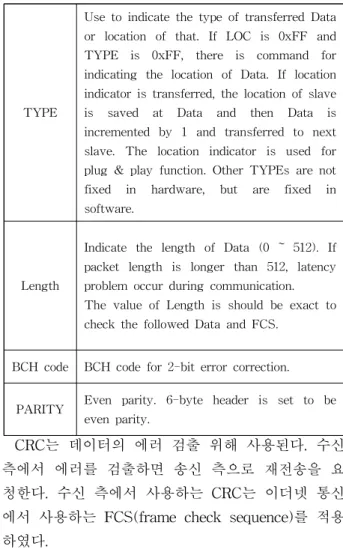

1) 패킷과 오류 검출

COM블록은 오류 정정 기능을 구현하기 위해 패킷 단위로 통신한다. 그림 5. 는 패킷의 구조를 표시한 것이다.

Fig. 5. Structure of packet 그림 5. 패킷의 구조

하나의 패킷은 크게 idle, header, data, FCS(CRC) 로 나누어진다. 각 패킷은 시작할 때 수신 측의 데이터 에러 검출을 위해서 20-bit의 idle 구간이 필요하다. 표 4. 는 header의 구성을 보여 준다.

Table 4. The configuration of header 표 4. header의 구성

CRC는 데이터의 에러 검출 위해 사용된다. 수신 측에서 에러를 검출하면 송신 측으로 재전송을 요 청한다. 수신 측에서 사용하는 CRC는 이더넷 통신 에서 사용하는 FCS(frame check sequence)를 적용 하였다.

2) 통신을 위한 data의 형식

Data의 형식은 그림 6. 과 같이 UART의 바이 트 코드와 동일하다.

Fig. 6. The form of data for communication 그림 6. 통신 data 형식

UART의 바이트 코드는 START bit와 STOP

bit가 있고 통신하지 않는 구간 동안에는 data

line을 ‘1’로 유지하는 특성이 있다. 이 특성을 이

용해서 plug & play기능과 에러 보정 등의 기능

을 구현할 수 있다. 10-bit이상 1이 연속으로 발

생하면 idle 상태임을 알 수 있고, idle에서 0이 발

생하면 START임을 알기 때문에 그 때부터는 다

시 정상적인 통신을 수행할 수 있다. 시리얼 통신

의 큰 문제점은 오류가 발생하면 연속해서 발생 한다는 점이지만 UART의 START/STOP bit가 이러한 경우를 방지할 수 있다. START/STOP bit가 없으면 그 만큼 통신의 속도를 높일 수 있 지만 기능 구현이 대단히 어렵게 된다.

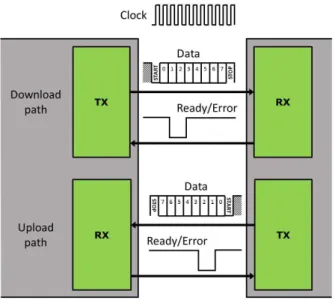

3) COM블록의 통신 방식

그림 7. 은 COM블록의 통신 방식을 보여준다.

Fig. 7. The communication method of COM block 그림 7. COM 블록의 통신 방식

Fig. 8. The error in packet transmission 그림 8. 패킷 전송에서 오류가 발생한 경우

TX쪽에서는 RX로 clock과 data를 전송하고, RX는 TX로 Ready/Error신호를 보낸다. 그림 8.

은 패킷 전송에서 오류가 발생하였음을 TX로 알 려주는 방법을 표시한 것이다. TX는 전송을 시작 하기 전에 반드시 Ready/Error 신호를 확인하여 1일 때만 패킷을 전송한다. 패킷 전송 중에 Ready/Error신호가 0이 되면 TX는 전송을 중단 하고 재전송 한다. FCS에서 에러가 발생한 경우 는 그림 8. 의 두 번째 에러와 같이 패킷 전송이

완료된 후에 발생한다. TX는 패킷 전송 후에 8-bit구간 동안 발생한 에러는 FCS 에러로 처리 하고, 이 전 패킷을 재전송해야 한다. 패킷의 구 조에서 idle이 20-bit가 필요한 이유는 이러한 FCS error의 처리 때문이다.

나. COM 블록 구성

그림 9. 는 COM블록의 단방향(업로드 혹은 다 운로드)을 위한 구조이다. COM블록은 업로드와 다운로드가 있어야하기 때문에 COM블록에는 아 래의 블록도가 두 개 있다. 아래의 블록 도는 RX, TX, CPU IF로 구성되는데 각각의 블록에는 512 바이트 SRAM과 헤더 레지스터로 구성된 버퍼들 이 있다. RX는 수신한 데이터를 CPU IF와 TX로 전달할 수 있다. TX는 RX 또는 CPU IF에서 받 은 데이터를 다음 단의 슬레이브 또는 메인 모듈 로 전송한다. 2개의 버퍼를 가진 RX와 달리 TX 는 한 개의 버퍼만으로 구성되어 있는데 내부에 서의 전송은 외부 전송 신호보다 32배 정도 빠르 기 때문에 한 개의 버퍼로 처리할 수 있기 때문 이다.

Fig. 9. The communication block of module 그림 9. 모듈의 통신 블록

CPU IF에는 RX용 버퍼와 TX용 버퍼가 있다.

전송할 data를 TX 버퍼에 저장한 다음 전송하도 록 레지스터를 설정하면 TX의 버퍼로 전달된다.

RX 버퍼에는 RX가 수신한 데이터가 저장되고,

CPU는 CPU IF의 RX 버퍼를 통해서 패킷을 받

는다.

다. 모듈간의 체인 구성

그림 10. 은 SoC를 이용한 각 모듈을 체인에 연결 했을 때를 표시한 것이다. 1개의 체인에 연 결된 모듈들은 동일한 clock을 이용하는 데, 모듈 을 통과할 때마다 clock에 약간의 딜레이가 더해 짐에 유의해야 한다. 패킷 헤더의 LOC가 8-bit이 고 0xFF는 위치확인 명령에 사용되어 사용할 수 없기 때문에 체인에는 1개의 메인 모듈과 최대 254개의 슬레이브 모듈이 연결될 수 있다.

Fig. 10. A chain connection of SoC chip for communication block

그림 10. 통신 블록을 적용한 SoC 칩의 1 체인 연결

Fig. 11. Two chain connection of SoC chip for communication block

그림 11. 통신 블록을 적용한 SoC 칩의 2 체인 연결

그림 11. 은 2개의 체인을 구성하는 경우를 표 시한 것이다. 메인 모듈에 적용된 COM블록의 업 로드, 다운로드 통로가 내부에서 끊어져서 체인간 의 데이터 전송은 이루어지지 않음을 알 수 있다.

그림에는 chain0과 chain1이 같은 clock을 사용하 도록 표시되었지만 실제로는 chain0는 chain1의 분주된 clock을 사용한다. 그림 12. 는 Ready/Error신호를 이용해서 plug & play기능을 실행하는 것을 표시한 것이다.

Fig. 12. Ready/Error signal of plug & play

그림 12. Plug & play 지원을 위한 Ready/Error 신호

Plug & play를 위해서 TX 의 Ready/Error신호 는 그림 12. 에서와 같이 풀-다운 저항을 연결한 다. 만약 RX와의 연결이 끊어지면 Ready/Error 신호가 ‘0’으로 변경되는데, TX 는 Ready/Error 신호가 2048 cycle 이상 ‘0’이면 연결이 끊어짐으 로 판단하고 데이터를 전송하지 않고 모든 TX 전송 요청을 무시한다. 그림 12. 의 오른쪽 그림 은 끊어진 상태에서 연결된 경우를 표시한 것이 다. 이 경우에도 2048 cycle이상 Ready/Error신호 가 ‘1’임을 이용해서 연결됨으로 판단한다. 연결이 끊어진 상태에서 연결 상태로 변경되었을 때 업 로드 통로의 RX는 새로 연결된 신호들에서 발생 한 노이즈에 의해서 오동작하는 것을 방지하여야 한다. 그래서 COM블록은 연결 상태로 변경된 후 에 정상적으로 위치 확인 명령이 전송되어야 업 로드 통로가 동작할 수 있도록 설정해야 한다.

3. 구현

SoC 칩은 130nm 공정으로 개발되었다. 그림 13.

은 설계된 SoC의 레이아웃을 보여 준다. 설계된 SoC의 각 블록의 특징에 대한 설명은 앞서 언급 되었던 표 1, 2, 3. 과 같다.

Fig. 13. layout for design SoC

그림 13. 설계된 SoC의 레이아웃

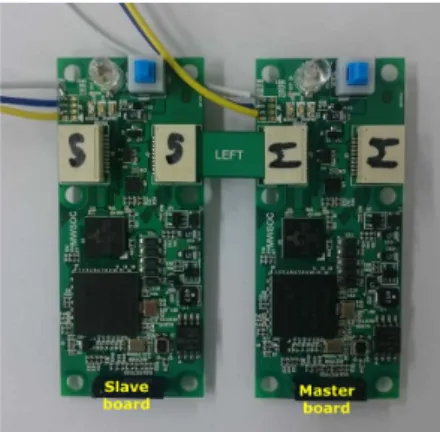

개발된 칩은 225-ball BGA 패키지를 사용하였고 패키지의 크기는 13mm x 13mm이다. SoC를 테 스트하기 개발된 평가 보드는 보조 보드와 메인 보드로 구성된다. 메인 보드는 그림 14. 와 같이 SoC칩과 32M byte SDRAM, 128-M bit 시리얼 플래시, 리셋회로, SoC의 클럭을 위한 오실레이터 들로 구성되고, 나머지 인터페이스들은 보드의 주 변 부분에 연결할 수 있는 커넥터만 배치하였다.

메인보드에는 전원관련 회로가 없고 보조 보드에 서 공급된다. 제작된 메인 보드는 스위치를 이용 해서 메인 또는 슬레이브 모듈로 설정할 수 있다.

Fig. 14. Main board for SoC evaluation

그림 14. 제작한 SoC 칩의 평가 보드 중 메인 보드

Fig. 15. Peripheral board for SoC evaluation 그림 15. 제작한 SoC 칩의 평가 보드 중 보조 보드

그림 15. 는 보조 보드이다. 보조 보드에는 LCD 를 부착할 수 있고, SD card 슬롯, USB PHY와 커넥터, UART 인터페이스, 이더넷 PHY, 트랜스 포머, 커넥터가 있고 전원회로가 있다. 전원회로 는 5 V입력을 받아서 메인 보드에서 필요로 하는 1.2 V, 3.3 V전원들을 만들어낸다. 그림 16. 은 보 조 보드에 메인 보드를 장착해서 메인 모듈을 구 성한 것이다. 이 보드를 이용해서 SoC의 동작을 테스트하고 검증하였다. 평가보드는 프로그램 개 발을 위해서 만들어진 것이기 때문에 디버거 포 트를 이용해서 PC와 연결하고 개발용 툴 체인과

연동이 되면 프로그램 개발을 시작할 수 있다. 이 클립스 환경을 기반으로 한 SPARC CPU용 개발 툴을 이용하여 CPU의 동작과 각 종 인터페이스 의 동작을 테스트하였다.

Fig. 16. Main module consisting of main board and peripheral board

그림 16. 메인 보드와 보조 보드로 구성한 메인 모듈

그림 17. 은 메인 모듈에 LCD를 부착하고, 온도 센서와 습도센서를 연결해서 동작을 검증하는 것 이다. LCD에 온도와 습도가 디스플레이 되고 있 음을 확인할 수 있다.

Fig. 17. Verification of operation of main module using temperature and humidity sensor

그림 17. 온도와 습도 센서를 이용한 동작 검증

메인 보드에는 메인 모듈과 슬레이브 모듈을 연

결하는 커넥터가 2개 있다. 이 커넥터를 이용해서

메인 모듈과 슬레이브 모듈을 그림 18. 과 같이

연결할 수 있다. 그림과 같이 연결하면 슬레이브

모듈에 1개의 연결 커넥터가 연결되지 않았는데,

이 커넥터를 다음 슬레이브에 연결할 수 있다. 이

렇게 계속 연결을 확장해서 체인을 구성할 수 있

다. 메인 보드 자체는 전원회로가 없다. 그래서

메인 보드로만 구성된 슬레이브 모듈은 마스터

모듈과 연결되는 케이블을 통해서 전원을 공급받

도록 설계되었다.

Fig. 18. Connection of master and slave 그림 18. 마스터와 슬레이브의 연결

평가보드를 이용해서 SoC 칩의 검증을 마치고, 이를 기반으로 그림 19. 와 같이 실제 제품에 적 용할 수 있도록 작은 크기의 모듈용 보드를 개발 하였다. 이 보드의 크기는 3cm x 7cm이다. 작은 보드에 적합하도록 부품들도 크기가 작은 것으로 선정하였다. 이 모듈 보드는 평가보드의 메인 보 드와 부품 구성의 거의 동일함을 알 수 있다. 평 가 보드에서는 전원회로가 보조 보드에 포함되어 있었지만 모듈 보드는 전원회로를 가지고 있고, 소형 배터리로 동작하도록 설계하였다. 평가 보드 에서와 마찬가지로 기본 모듈 보드는 저항 설정 을 이용해서 마스터 또는 슬레이브로 동작하도록 설정할 수 있다.

Fig. 19. Small-sized modules 그림 19. 작은 크기의 모듈

모듈 보드는 센서모듈이나 통신모듈로 동작해야 하는데 그림 19. 의 기본 모듈보드에는 센서나 통 신용 부품이 없다. 그래서 센서나 통신용 부품은 별도의 작은 보드로 만들어서 기본 모듈 보드의 sub-board 커넥터로 연결해야 한다. sub-board의 크기는 3cm x 4cm의 규격으로 제작하도록 한다.

Fig. 20. Placement of main board and sub board 그림 20. 메인 보드와 서브 보드의 배치

서브 모듈보드에는 센서나 통신용 부품을 배치하 고 그림 20. 과 같이 기본 모듈 보드에 장착될 수 있도록 정확한 규격으로 PCB를 설계해야 한다.

기본 모듈 보드의 부품들 높이가 높지 않아서 여 러 층의 서브 모듈 보드를 쌓는 것도 가능하다.

그림에서와 같이 높이가 약간 있는 모듈간의 커 넥터나 LED, 전원스위치는 서브 모듈보드와 겹치 지 않도록 설계되어 있다. 기본 모듈보드를 이용 해서 만들어지는 마스터와 슬레이브는 그림 21.

과 같이 연결용 PCB를 이용해서 연결된다.

Fig. 21. Connection of master and slave board 그림 21. 마스터 보드와 슬레이브 보드의 연결

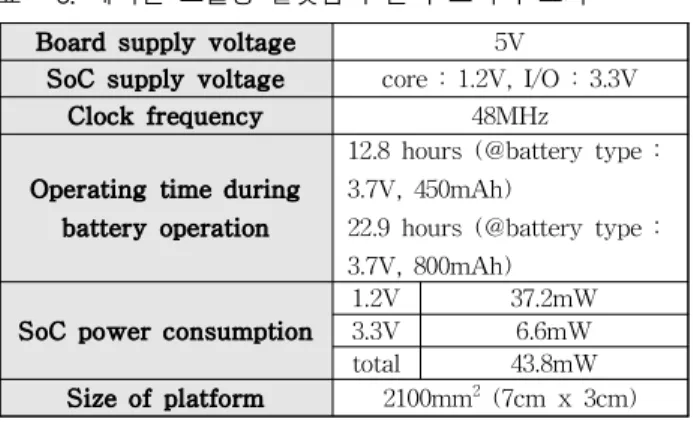

제작된 웨어러블 모듈형 플랫폼의 전력 소비와

사용시간, 그리고 플랫폼의 크기는 표 5와 같다.

Board supply voltage 5V

SoC supply voltage core : 1.2V, I/O : 3.3V

Clock frequency 48MHz

Operating time during battery operation

12.8 hours (@battery type : 3.7V, 450mAh)

22.9 hours (@battery type : 3.7V, 800mAh)

SoC power consumption 1.2V 37.2mW

3.3V 6.6mW

total 43.8mW

Size of platform 2100mm

2(7cm x 3cm)

Sung Hoon Park

1992 : BS degree in Electronics Engineering, Pusan National University.

1994 : MS degree in Electircal Engineering, Korea Advanced Institute of Science and Technology.

1994 ~ 1999 : Senior Engineer, LG Semicon 1999 ~ 2000 : Senior Engineer, Hynix

2000 ~ : Vice President, ZARAM Technology Table 5. Power consumption and size of

fabricated modular platform

표 5. 제작된 모듈형 플랫폼의 전력 소비와 크기

III 결론

다양한 분야와 환경에서 필요에 따라 기능을 쉽 게 교환하고 조립이 가능한 모듈형 웨어러블 플 랫폼이 제안되었다. 제안된 플랫폼의 SoC는 32-bit RISC CPU (MENSA), 32-bit Symmetric Multi-core processor (SPARC V8), 그리고 16-bit DSP 2 array (2개의 16-bit CDSP16)으로 구성되고 여기에 필요에 따라 센서 모듈과 통신 모듈이 2개의 체인을 구성한다. 2개의 체인 중 한 개는 통신 모듈들을 연결하고, 나머지 한 개의 체 인에는 센서 모듈들을 연결하여 체인 clock 주파 수를 낮게 설정할 수 있게 되고 전력소비를 최적 화 할 수 있다. SoC 칩은 130nm 공정으로 개발 되었고 온도와 습도 센서를 이용하여 제안된 모 듈형 웨어러블 플랫폼의 기능의 동작을 테스트 하였다. 또한 실제 제품에 적용할 수 있도록 작은 크기의 모듈을 설계하여 마스터 보드와 슬레이브 보드를 구성하였다.

References

[1] T. Shimizu, et al . "A multimedia 32 b RISC microprocessor with 16 Mb DRAM", in Digest of Technical Papers. 42nd International Solid-State Circuits Conference (ISSCC) , Feb.

1996.

DOI : 10.1109/ISSCC.1996.488577

[2] E. MuraliKrishnan, E. Gangadharan, P.

NirmalKumar. "FPGA Based Symmetric Multi-core Processors for Optimized Performance of H.264 Encoder", in Advances in Recent Technologies in Communication and Computing (ARTCom), 2010 International Conference on , Oct. 2010.

DOI : 10.1109/ARTCom.2010.106

[3] Po-Chih Tseng, Chi-Kuang Chen, Liang-Gee Chen. "CDSP: an application-specific digital signal processor for third generation wireless communications", IEEE Transactions on Consumer Electronics., vol 47, on. 3, pp.672 – 677, Aug. 2001.

DOI : 10.1109/30.964162

BIOGRAPHY