碩 士 學 位 論 文

플 라 이 백 컨버 터 의

전도 노 이즈 해 석 에 관 한 연구

A St udy on t he Ana lys i s of Conduct ed Emi ss ion Noi se of Flyback Conver t er

國 民 大 學 校 大 學 院 電 子 工 學 科

金 泰 鎭

플 라 이 백 컨버 터 의

전도 노 이즈 해 석 에 관 한 연구

A St udy on t he Ana lys i s of Conduct ed Emi ss ion Noi se of Flyback Conver t er

指 導 敎 授 洪 成 洙

本 論 文 을 碩 士 學 位 請 求 論 文 으 로 提 出함

2 0 0 1年 6 月 日

國民 大 學 校 大 學 院

電 子 工 學 科

金 泰 鎭

2 000

金 泰 鎭 의

碩 士 學 位 請 求 論 文 을 認 准 함

2 0 0 1年 6 月 日

審 査 委 員 長 司 空 石 鎭 印 審 査 委 員 洪 成 洙 印 審 査 委 員 安 鉉 植 印

國民 大 學 校 大 學 院

감 사 의 글

본 논문이 완성되기까지 따뜻한 격려와 애정으로 지도하여 주신 사공 석진 교수님께 진심으로 감사드립니다. 학문의 바른 길을 가르쳐 주시 고 끊임없는 지도와 편달을 아껴주시지 않으신 홍성수 교수님께 무한한 감사를 드립니다. 그리고 심사를 해주신 안현식 교수님께 감사를 드립 니다.

본 연구를 수행하는 동안 도움을 주신 회로 및 시스템 실험실 박사과 정의 최태섭 선배님, 안인수 선배님, 송석호 선배님, 석사과정의 석철, 상진, 승훈, 연상, 학부생의 은범, 동열, 필준, 성우, 승곤이에게 감사를 드립니다. 항상 옆에서 아낌없는 도움을 주신 일수형과 끝까지 편집을 도와준 영웅이, 시작부터 아낌없는 도움을 준 박사과정의 정동열에게 특별히 감사드립니다. 소중한 나의 대학 동창들과 류동균, 김인겸, 권덕 종, 나의 십년지기 경일, 상호, 재윤이에게 감사를 드립니다.

그리고, 항상 제 옆에서 힘과 도움을 주신 두 분 형님과 누님 또한 두 분 형수님과 매형, 조카들 그리고 옆에서 힘이 되어준 지수에게 감 사의 말을 전하며, 마지막으로 끝없는 믿음과 사랑을 베풀어주신 아버 님과 어머님께 이 논문을 드립니다.

목 차

국문 요약

Ⅰ. 서 론 ……… 1

Ⅱ. 기생 성분 모델링 ……… 3

2.1 P CB 패턴의 기생 성분 모델링

……… 3

2.1.1 기생 인덕턴스 모델링

……… 4

2.1.2 기생 캐패시턴스 모델링

……… 5

2.1.3 기생 저항 모델링

……… 7

2.2 능동 소자의 모델링

……… 9

2.3 수동 소자의 모델링

……… 11

2.3.1 캐패시터의 모델링

……… 12

2.3.2 인덕터의 모델링

……… 13

2.3.3 트랜스포머 모델링

……… 14

2.4 LISN의 모델링

……… 15

Ⅲ. 전도 노이즈의 해석 ……… 17

Ⅳ. 실험 결과 및 검토 ……… 26

4.1 플라이백 컨버터의 설계

……… 26

4.1.2 트랜스포머 설계

……… 26

4.1.3 입출력 캐패시터 설계

……… 30

4.1.3.1 입력 캐패시터 설계

……… 30

4.1.3.2 출력 캐패시터 설계

……… 31

4.1.4 반도체 소자 선정

……… 33

4.2 시뮬레이션 회로 구성

……… 33

4.2.1 수동 소자 임피던스 측정 및 모델링

……… 33

4.2.1.1 캐패시터 측정 및 모델링

……… 33

4.2.1.2 인덕터 측정 및 모델링

……… 35

4.2.1.3 트랜스포머 측정 및 모델링

……… 36

4.2.2 P CB 패턴의 기생 성분 추출 및 모델링

……… 38

4.3 실험 결과

……… 40

4.3.1 시뮬레이션 결과

……… 40

4.3.2 측정 결과

……… 43

4.4 결과 분석

……… 45

Ⅴ. 결 론 ……… 47

참고 문헌 ……… 48

Ab str act ……… 49

국 문 요 약

본 논문에서는 전원 공급기 설계 단계에서 전도 노이즈에 대한 분석 을 할 수 있는 모델링을 제시하며. 또한, 전도 노이즈를 감소시키기 위 해 P CB 의 패턴 구성 등 설계시 주의해야 할 사항들을 제안 한다.

이를 위해 먼저 전도 노이즈에 영향을 줄 수 있는 요소들(P CB 패턴, 수동 소자 및 능동 소자)에 대한 회로 모델 구성 방법을 제시 한다.

이후, 구해진 회로 모델들을 기반으로 전체 전도 노이즈 시뮬레이션 회로 모델을 구성하여, 플라이백 컨버터의 전도 노이즈에 대한 노이즈 소스원과 커플링 경로를 분석 한다.

시뮬레이션 파형과 스펙트럼 분석기로 측정 결과의 비교 자료를 제시 하고자 한다. 제시된 사항을 검증하기 위해서 29W 플라이백 컨버터를 설계 한다.

Ⅰ . 서 론

최근 몇 년에 걸쳐 전원 공급기 설계에 대한 많은 연구들이 진행되고 있다. 이들 연구중 대부분은 전력단 T opology , 제어 회로 모델링, 특성 해석, 자기(M agn etic) 소자 최적화 등 전원 공급기 자체의 성능에 대한 것들이 대부분이었다. 하지만, 전원 공급기의 고주파 스위칭으로 인해 발생하는 EM I(Electro- M agn etic Int erferen ce) 문제에 관한 연구는 상 대적으로 미비하다.

그러나, 전자파 노이즈는 시스템의 성능 및 신뢰성을 좌우하는 결정 적인 요소이다. 시스템에서 고려할 수 있는 전자파 노이즈는 크게 두 가지로 나눌 수 있다. 첫째는 RF (Radio F r equ ency ) 신호로 인한 방사 노이즈이고, 둘째는 정보통신 시스템에 전력을 공급하는 SM P S (S w it ch ed M ode P ow er S upply )가 전압을 조절하기 위하여 전력 소자 인 M OSF ET 의 온- 오프 스위칭 시에 발생하는 전도 및 방사 노이즈이 다.

컨버터의 전력 밀도를 높이기 위한 끊임없는 노력으로, 스위칭 주파 수는 점점 높아지고 있으며, 이로 인해 전자파 노이즈 특성은 점점 나 빠지고 있다. S M P S 에서 생성된 잡음은 주변 장비에 E M C (Elect r o - M agn etic Com pat ibilit y ) 문제를 야기시킴은 물론, 전원 공급 기 자체의 제어 회로의 동작을 중단시킬 수도 있다.

더불어, 시스템은 급속한 속도로 고속 집적화 되고 있으며 EM I 및 E M C 규정은 최근 몇 년 사이 까다롭게 변화하고 있다. 따라서, 시스템 의 신뢰성은 전원 공급기에서 발생하는 잡음의 정도에 크게 의존하게 되었다. 하지만, 이러한 중요성에도 불구하고 기존의 전원 공급기 설계 방식은 Cut - and - T rial 방식에 의존하고 있다. 이로 인해 개발 기간이 연장됨은 물론, 최악의 경우 시스템 개발 자체의 실패의 가능성이 더욱

커지게 된다.

그러므로 실제 하드웨어를 제작하기 전에 미리 예상되는 노이즈를 시뮬레이션 소프트웨어를 사용하여 분석하고, 이에 대한 대책을 수립하 는 것이 개발 기간 단축 및 시스템 전체의 신뢰성을 높이는 주된 방법 이 된다. 이를 위해, 전원 공급기 설계 단계에서 예상되는 노이즈를 규 명할 수 있는 이론적 및 방법적 접근 방식이 제공되어야 한다. [1] 은 이러한 추세에 따라 P CB (Printed Circuit Boar d ) 상의 기생 요소들이 전도 노이즈에 미치는 영향을 분석할 수 있는 가능성을 제시한 논문이 다.

그러나 아직까지 절연형 컨버터에 대해서는 시뮬레이션을 통한 전도 노이즈 예측에 대한 연구가 미비하므로, 본 논문에서 다음과 같은 사항 들에 대해 연구를 진행하였다.

첫째, 전원 공급기 설계 단계에서 전도 노이즈에 영향을 미칠 수 있 는 P CB 패턴, 수동 소자 및 능동 소자에 대한 전도 노이즈를 정확하게 예측할 수 있는 회로의 모델을 제시한다.

두 번째, 모든 기생 성분이 포함된 전도 노이즈 회로 모델을 이용하 여, 플라이백 컨버터에 대한 전도 노이즈의 소스원과 커플링 경로를 규 명하고자 한다. 또한 전도 노이즈의 커플링 경로에 대한 전도 노이즈를 예측하기 위한 P spice 회로 모델링을 통해서 전도 노이즈에 지배적인 영향을 미치는 요소들을 규명하여 P CB 설계 및 소자 선택시 중요하게 작용하는 매개 변수들을 제시한다.

마지막으로 시뮬레이션시 P CB 패턴 전체 기생 성분을 포함시킨 회 로와 주요 커플링 경로의 기생 성분을 포함시켰을 때의 파형을 비교 분 석 후 시뮬레이션 시간을 단축시켜서 회로를 분석할 수 있는 방안을 제

Ⅱ . 기 생 성 분 모 델 링

모든 소자, 혹은 P CB 패턴상에는 일정량의 기생 성분들이 존재한다.

기생 성분이란, 소자내 혹은 소자와 소자 사이에 존재하는 기생 용량으 로서 소자가 갖는 본래의 기능을 방해하는 성분들을 의미한다. 대표적 인 예로써, 캐패시터의 직렬 등가 저항(Equiv alent S eries Resist an ce, E SR ), 인덕터의 기생 캐패시턴스 등을 들 수 있다. 수동 소자 뿐만 아 니라, 능동 소자 혹은 P CB 패턴상에도 이처럼 원치 않는 기생 성분들 이 존재하게 된다.

전달 지연, 공진 등 기생 성분으로 인해 발생하는 현상들은 시스템 동작 특성을 저하시킬 뿐만 아니라, 전도 노이즈가 발생하고 커플링 경 로를 제공하는 주 요인으로 작용한다. 따라서, 전원 공급기의 전체 전도 노이즈를 분석하기 위해서는 무엇보다 먼저 설계에 사용된 각 소자 및 구성된 P CB 패턴상에 존재하는 기생 성분들을 추출해야 한다.

2.1 P CB 패턴의 기생 성분 모델링

P CB 패턴상의 기생 성분에 대한 분석은 이미 많은 연구가 진행되어 있으며, 이를 손쉽게 수행할 수 있는 소프트웨어들도 소개되어 있다.

P CB 패턴의 기생 성분은 저항, 인덕턴스, 캐패시턴스로 해석할 수 있 다.

저주파에서 P CB 패턴은 기본적으로 저항 성질을 나타나게 된다. 그 러나, 주파수가 높아지면서 P CB 패턴은 점점 인덕터의 성질을 나타내 게 된다. 이러한 현상은 P CB 의 접지 구성에 따라 큰 편차를 보인다.

통상 100[㎑] 이상의 주파수 대역에 대해 P CB 패턴은 인덕터의 성질을 강하게 나타낸다. 일반적으로는 가청 주파수 대역 이상에서는 P CB 를

유도성 소자로 해석하는 것이 원칙이다.

P CB 패턴상에 존재하는 기생 캐패시턴스는 기본적으로 주파수가 높 아짐에 따라 낮은 임피던스를 나타내기 때문에 기생 인덕턴스에 비해 지배적인 성분은 아니다. 그러나, 기생 인덕턴스와 더불어 공진 현상을 일으켜 고주파의 노이즈 성분을 발생시키는 요소로 작용하기 때문에 이 에 대한 분석이 필요하다.

이 절에서는 P CB 패턴상에 존재하는 각각의 기생 성분들의 모델링 에 대해 알아본다.

2.1.1 기생 인덕턴스 모델링

기생 인덕턴스 계산은 모델링된 P CB 경로의 전류 흐름을 분석함으 로써 이루어진다. 일반적으로, 인덕턴스는 폐전류 경로에 대해 다음과 같은 방식으로 정의된다.

- 자속 링크와 전류 흐름에 의한 정의 : = L i

- 시변 전류와 전압 변화에 의한 정의 : V = L d i

dt

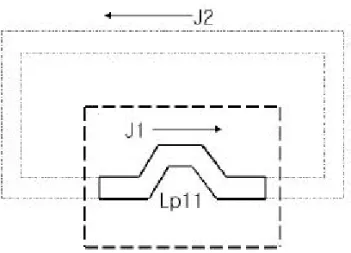

그러나, 개방 전류 경로에 대한 인덕턴스 또한 고려되어야 한다. 이를 부분 인덕턴스라 정의한다. 그림 2- 1 와 같이 굵은 실선 부분만으로 구 성된 도체의 경우 전체 인덕턴스는 루프 각 영역의 인덕턴스를 포함한 모든 인덕턴스의 합과 같다.

그림 2- 1. 부분 인덕턴스 개념도

F ig . 2- 1. Con ceptu al Dia gr am of P art ial In du ct an ce

인덕턴스 중 굵은 실선으로 표시된 실질적인 경로 부분만이 부분 인 덕턴스 계산에 모델링되기 때문에 회귀 전류의 효과는 무시된다. 물리 적으로, 부분 인덕턴스는 회귀 전류 경로를 명시하기 어려운 경우에 사 용되는 개념이다. 수식적인 표현은 식 (2- 1)에서 나타내는 것과 같다.

L T ota l = Lp11 + L p12+ Lp22+ Lp21

=

v1a1・J1d V +

v1A 1・J2 d V +

v2A 2・J2d V +

v2A 2・J1d V

(2- 1)

2.1.2 기생 캐패시턴스 모델링

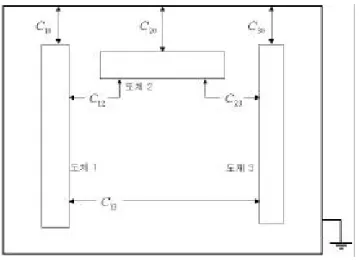

기생 캐패시턴스의 모델링은 P CB 경로상의 전압/ 전하 분포를 분석함 으로써 얻어진다. P CB 상에 존재하는 도체간의 전압/ 전하 분포는 식 (2- 2) 와 같이 행렬 형태로 나타낼 수 있다. [2] 캐패시턴스 행렬은

P CB 경로들간에 발생하는 전하의 커플링, 즉, 도체내에 존재하는 전하 와 전압간의 관계를 나타낸다. 그림 2- 2 와 같은 형태로 P CB 상에 세 개의 도체가 존재한다고 가정해 보자. 외부 경계를 기준으로 했을 때 각 도체내에 존재하는 전하는 식 (2- 2) 와 같이 나타낼 수 있다.

그림 2- 2. 기생 캐패시턴스 개념도

F ig . 2- 1 Con ceptu al Diagr am of P ar a stic Capacit an ce

Q1 = C10V1+ C12( V1- V2) + C13( V1- V3)

Q2 = C20V2+ C12( V2- V1) + C23( V2- V3)

Q3 = C30V3+ C13( V3- V1) + C23( V3- V2)

(2- 2)

각 도체에 분포된 전압을 1[V ] 라 하고 식 (2- 2) 를 캐패시턴스 행렬 식으로 나타내면 식 (2- 3) 와 같다.

도체(P CB 경로)가 n 개 있는 경우라면 n×n 행렬이 전하 Q 와 전압 V 의 관계를 나타내게 된다. 이 때, 행렬내의 대각 요소들은 한 도체로

Q1

Q2

Q3

=

C10+ C12+ C13 - C12 - C13

- C12 C20+ C12+ C23 - C23

- C13 - C23 C30+ C13+ C23

V1

V2

V3

(2- 3).

부터 모든 도체와의 캐패시턴스의 합을 나타내고, 비대각 요소들은 각 각의 개별 도체와의 캐패시턴스를 의미한다. 이 행렬은 각각 대칭을 이 루게 되는데 이는 두 도체간의 상호 용량은 같다는 것을 의미한다.

2.1.3 기생 저항 모델링

기생 저항 모델링은 도체에 흐르는 전류와 전압 강하 사이의 관계에 의존한다. 일정한 전속 밀도가 흐르는 도체내의 저항 성분에는 다음과 같은 관계가 성립한다.

R =

VJ・ E d V , E = J

(2- 4 )

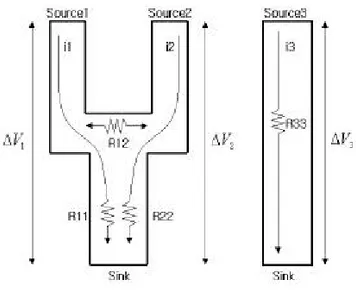

예를 들어, 그림 2- 3 과 같은 형태의 도체가 존재하는 경우 각 전압 강하와 전류 사이의 관계에 의해 구해지는 저항 성분들은 식 (2- 5) 와 같이 주어진다.

여기서 R1 1, R2 2, R3 3 와 같은 대각 요소들은 각 전류 경로의 자기 저 항을, R1 2 와 같은 요소들은 전류 경로 사이에 존재하는 저항 성분을 의미한다. 서로 접하는 면을 가지고 있지 않은 도체들 사이에서 저항은 0 이 된다.

그림 2- 3. DC 저항 개념도

F ig . 2- 3 . Con ceptu al Diag r am of D C R esist an ce

V1

V2

V3

=

R11 R12 0 R12 R22 0 0 0 R33

(2- 5 )

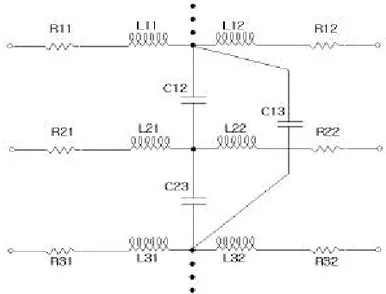

앞에서 설명된 모든 기생 성분들의 모델을 포함하는 P CB 패턴의 모 델링 결과를 그림 2- 4 에 보이고 있다. 이후 설명되겠지만, P CB 패턴 상의 기생 용량들은 A n soft 사의 Spicelink 를 이용하여 모델링된다. 이 에 관한 자세한 내용은 4장에서 설명한다.

그림 2- 4. P CB 패턴의 기생 성분의 모델링 개념도 F ig . 2- 4 T ot al P ar a sit ic cir cuit con figu r e

2.2 능동 소자의 모델링

전원 공급기에는 다이오드와 스위치용 M OSF ET 와 같은 전력 소자 가 사용된다. 이들의 스위칭 특성은 M OS F ET 의 온/ 오프시 발생되는 d i/ d t 혹은 d v/ d t 를 결정하는데 중요한 역할을 하기 때문에, 전도 노

이즈를 예측하는데 중요한 부분을 차지하고 있다. 본 논문에서는 P Spice 라이브러리에서 제공하는 모델을 사용하여 전도 노이즈를 예측 하는 시뮬레이션에 포함시켰다.

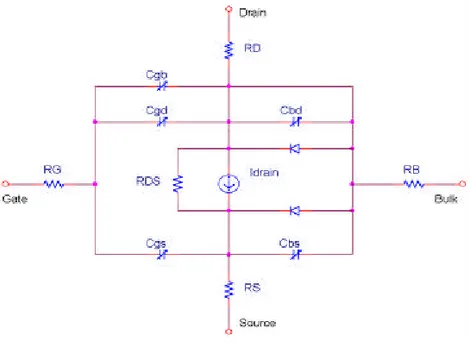

전력 M OS F ET 의 P Spice 모델을 살펴보면 다양한 기생 성분이 나 타나게 되는데, 그 중에서 Cd s 값이 M OSF ET 의 턴 오프시 발생되는 공진 현상을 일으키는 원인 중의 하나이다. 이에 대한 논의는 3장에서 더 자세히 설명 한다.

그림 2- 5 는 P Spice 에서 제공되는 M OSF ET 의 등가 모델을 나타내 었다.

그림 2- 5 M OSF ET 의 등가 모델 F ig . 2- 5 E qu iv alen t M odel of M OS F E T

다이오드의 경우에는 스위칭 특성, 역회복 특성이 전도 노이즈를 해 석하는데 중요한 부분을 차지하고 있다. 그림 2- 6 은 P Spice에서 제공 하는 다이오드의 등가 모델을 나타내고 있다.

만일, 제조사에서 모델을 제시하지 않는 경우 측정을 통해 능동 소자 에 대한 모델링 하는 방법들도 존재하지만, 이는 본 논문과는 관련이 없으므로 이에 관한 언급은 피한다.

그림 2- 6 다이오드의 등가 모델 F ig . 2- 6 E quiv alent M odel of Diode

2.3 수동 소자의 모델링

P CB의 기생 성분 추출은 실제의 P CB가 나오기 전에 선행되어져야 하기 때문에 소프트웨어를 사용한 결과에 의존하게 된다. 능동 소자의 모델링 또한 실측에 의한 데이터들을 사용하기에는 고가의 장비 및 복 잡한 측정 과정을 요구하기 때문에 제조사에서 주어지는 모델링을 사용 하게 된다. 하지만, 수동 소자의 기생 성분 추출은 실제 상용 소자의 측 정을 통해 결과를 얻어낼 수 있다. 측정에는 범용적으로 사용되는 임피 던스 분석기(HP - 4395A ) 를 사용할 수 있다.

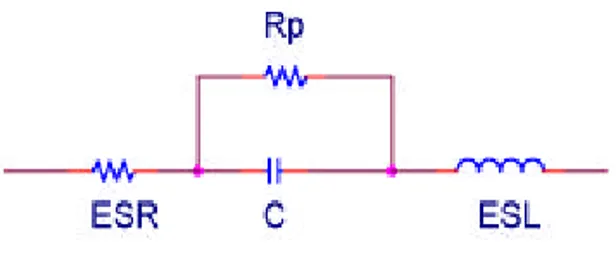

수동 소자 모델링은 기존에 발표되어 있는 많은 자료들이 제시되어 있다. 본 논문에서는 캐패시터에 대해 E SR 및 E SL 을 포함하는 형태 의 모델을, 인덕터에 대해서는 병렬 캐패시턴스 와 DC 저항을 포함하 는 형태의 모델을 사용 한다.

2.3.1 캐패시터의 모델링

플라이백 컨버터에서는 두 종류의 캐패시터가 있다. 먼저, 입력 A C 전류의 리플을 차단하기 위한 입력 캐패시터와 출력의 리플 전압을 제 거하기 위하여 출력 캐패시터에는 일반적으로 알루미늄 전해 캐패시터 가 사용된다. 그 외에 스너버와 제어 회로 등에는 세라믹 캐패시터가 사용된다. 두 종류의 캐패시터 모두 그림 2- 7 의 회로로 모델링이 된 다.

일반적으로 알루미늄 전해 캐패시터가 사용되는 입력 캐패시터의 경 우 1[㎒] 정도의 주파수 대역에서는 E SR 에 의한 저항 성분이 전체 임 피던스에 큰 영향을 주게 되고, 1 [㎒] 이상의 주파수 대역에서는 주파 수가 증가함에 따라 리드상에 존재하는 E S L (E quiv alent S er ies In du ct an ce ) 이 지배 성분이 된다. 이 모델에서 알 수 있듯이 이러한 기 생 성분들은 소자가 가지고 있는 고유의 특성이다. 따라서, 입출력 캐패 시터를 선정할 때에는 항상 이것을 염두에 두고 설계를 하여야 한다.

이 기생 성분 중 ES R 의 효과는 전체 전도 노이즈의 주요 원인이 되기 때문에 가능한 ES R 값이 낮은 부품을 사용할 필요가 있다. 이에 관한 논의는 3장에서 자세히 설명한다.

세라믹 캐패시터의 경우 보통 전해 캐패시터보다 훨씬 작은 캐패시턴 스를 갖기 때문에, 높은 자기 공진 주파수를 가지며, 이로 인해 고주파 에서 첨예한 병렬 공진 형태를 나타난다.

추가적으로 그림 2- 7 에 제시된 모델에서, 누설 저항으로 표현된 Rp 는 나머지 기생 성분들에 비해 그 영향이 크지 않기 때문에 이후 사용 될 시뮬레이션 회로에서는 생략한다.

그림 2- 7 캐패시터 등가 모델

F ig . 2- 7 E qu iv alen t M odel of In pu t Cap acit or

2.3.2 인덕터의 모델링

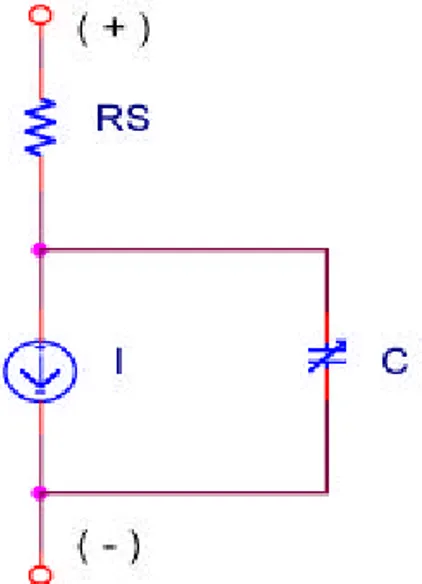

캐패시터와 반대로 인덕터의 경우 주파수 대역이 높아지면서 권선과 권선 사이에 존재하는 기생 캐패시턴스가 존재한다. 따라서, 인덕터의 구성에 따라 차이가 있기는 하지만, 보통 수십 [㎒] 이후의 주파수 대역 에서는 권선에 의한 캐패시터의 성분이 지배적인 성분이 된다.

따라서, 전도 노이즈를 해석하기 위해서는 그림 2- 8 과 같이 권선에 의한 기생 캐패시턴스를 포함하는 모델을 사용하여 시뮬레이션을 해야 한다. 그러나 E SR 은 인덕턴스의 값보다 상대적으로 작은 값이기에 노 이즈 시뮬레이션에서는 제외시킨다.

그림 2- 8 인덕터 등가 모델 F ig . 2- 8 E qu iv alent M odel of In du ct or

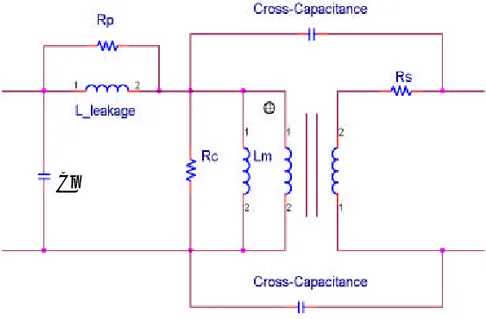

2.3.3 트랜스포머의 모델링

트랜스포머를 사용해야 하는 플라이백 컨버터와 같은 절연형 전원 공 급기의 경우에는 트랜스포머를 사용한다. 따라서, 트랜스포머의 정확한 모델링이 필요하다.

트랜스포머의 경우 인덕터 및 캐패시터와 달리 고주파 영역에서까지 정확히 트랜스포머의 동작을 설명하고 있는 모델이 정립되어져 있지 않 다. [4] 는 이러한 취지에서 트랜스포머의 고주파 영역 회로 시뮬레이션 모델을 제시하였다. 본 논문에서는 [4] 에서 제시한 모델을 사용하였다.

그림 2- 9 에 본 논문에 사용된 고주파 트랜스포머 모델을 제시하고 있 다.

지금까지 이루어졌던 수동 소자 모델링과 마찬가지로 트랜스포머 모 델링도 임피던스 측정 결과를 토대로 분석한다. 임피던스 측정은 1차측 에 대해 개방 회로 측정과 단락 회로 측정을 하고 개방 회로 측정 결과 로부터 저주파에서 1차측 권선의 DC 저항과, 자화 인덕턴스 Lm 을 구 하고, 단락 회로 측정 결과로부터 누설 인덕턴스와 2차측 권선으로부터 반사된 DC 저항을 계산한다.

문제가 되는 것은 1차측의 병렬 캐패시턴스 Cp 와 1차측과 2차측 사 이에 존재하는 캐패시턴스다. 이 값은 해석적인 방법을 통해 구해 내기 가 어렵다. 따라서, 본 논문에서는 시뮬레이션을 사용한 조절을 통해 이 값을 계산한다. 자세한 내용은 4장에서 소개된다. 해석적인 방법으로 권 선상의 기생 캐패시턴스를 구하는 내용은 좀 더 연구되어야 한다.

그림 2- 9. 트랜스포머 등가 모델 F ig . 2- 9 E quiv alen t M odel of T r an sform er

2.4 LISN 의 모델링

LISN (Lin e Im pedan ce St ab ilization N et w or k ) 은 노이즈 측정시, E M I 측정 규격을 만족시키기 위하여 전원 공급기와 입력 전원 사이에 설치된다. LIS N 의 설치 목적은 전원 공급기에서 발생된 노이즈가 전 원으로 전달되는 것을 억제하며, 또한 전원에 존재하는 노이즈가 측정 장치에 유입되어 발생하는 오차를 방지하기 위한 것이다.

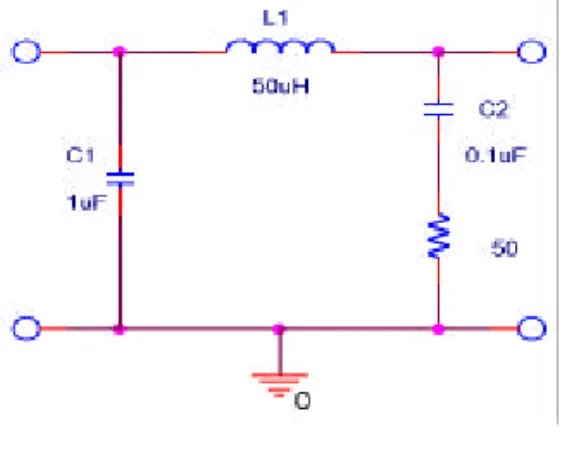

기본적으로 LIS N 은 A C 전원 입력 측과 전원 공급 측에 병렬 캐패 시터를 가지며, 전원 공급 측에는 표준 50[Ω] 임피던스가 연결된다. 그 리고, 전원 입력 측과 전원 공급 측 사이에는 인덕터를 삽입하여 전술 된 것처럼 입・출력간에 노이즈의 영향을 최소화시킨다. 제조사에 따라 인덕턴스값과 캐패시터의 값에 차이가 있기 때문에 측정에 사용할 LIS N 의 매뉴얼을 참조하여 이 값을 확인해야 한다.

Cp

그림 2- 11 은 전도 노이즈 잡음 측정에 사용될 EM CIS 사의 LN 2- 20A 의 LIS N (Lin e Im pedan ce St abilizat ion N et w or k ) 모델링을 나타낸다.

그림 2- 11. LISN 회로 모델 F ig . 2- 11. Cir cuit M odel of LISN

Ⅲ . 전 도 노 이 즈 의 해 석

플라이백 컨버터의 전도 노이즈를 시뮬레이션 소프트웨어로 해석하기 위해서는 정확한 P CB 패턴의 기생 성분들과 각 소자들의 기생 성분을 포함한 전체 회로 모델이 필요하다. 전체 회로의 각 부분을 구성하게 될 기생 성분의 모델링에 관한 내용은 2 장의 내용을 따른다.

이번 장에서는 2 장에서 추출된 각 소자내 기생 성분들의 영향에 의 한 노이즈 소스원과 커플링 경로의 구성에 대해 알아본다. 또한, 분석을 통한 결과로부터 노이즈 소스원을 최대한 억제하고, 커플링을 감소시키 는 방안에 대한 논의를 진행한다.

그림 3- 1 공통 모드와 차동 모드 전류

F ig 3 - 1 Com m on - m ode an d Differ en tial- m ode Cu rr en t s

전도 노이즈는 그림 3- 1에서 보는 바와 같이 공통 모드 및 차동 모 드 노이즈로 분리하여 해석할 수 있다. 이에 대한 이해를 위해 실제로 공급되는 교류 전원의 구성을 살펴보아야 한다. 실제 전원 공급기로 공 급되는 교류 전원은 Liv e, N eutral 과 접지의 세 단자 중 Liv e 단자와 N eu tr al 단자 양단의 전위차이다.

공통 모드 노이즈는 영전위 기준에 대해 Liv e 와 N eutral 에 대해 동 상인 노이즈를, 차동 모드 노이즈는 역상인 노이즈를 의미한다. 그림 3 - 1 에 공통 모드 및 차동 모드 노이즈를 각각 표현하였다.

실제의 노이즈는 언급된 바와 같이 차동 모드 및 공통 모드로 분리 해석할 수 있으며, 전체 노이즈는 이 둘의 벡터합 형태로 나타난다. 그 러나, 실제로 두 모드의 노이즈를 분리하는 것은 특별한 측정 장비 (N oise S ep er at or )를 필요로 한다. 본 논문에서는 노이즈를 분리하여 해 석하지 않고 전체 노이즈에 대한 논의만을 진행한다

첫번째 노이즈 소스원은 순시적으로 변하는 1차측 전류의 d i/ d t 이 다. M OSF ET 의 온/ 오프 천이 구간 동안에는 급격한 d i/ d t 의 변화율 을 갖는 전류가 흐르게 된다. 그림 3- 2 는 M OS F ET 의 턴 온시 전류 파형이다. 언급된 바와 같이 턴 온 순간에 고주파의 공진 현상이 발생 한다는 사실을 알 수 있다. 이 전류는 고주파 성분에 많은 에너지를 포 함하고 있다. 따라서, 이 전류가 입력단으로 커플링되어 전도 노이즈를 발생시키는 주원인으로 작용하게 된다. 이 전류의 커플링 경로는 다음 과 같다.

2차측 전류가 0 이 되었을 때, 2차측 다이오드의 역회복 기간 동안 트랜스포머의 누설 인덕턴스에 저장되었던 에너지가 다이오드의 접합

그림 3- 2 M OSF ET 의 턴- 온시의 전류 F ig . 3 - 2 Cur r en t in M OS F E T at T ur n - on

의 전류 턴온시 공진으로 나타나게 된다. 이 공진 전류는 최종적으로 P CB 패턴의 기생 캐패시턴스와 접지를 통해 전원 입력측으로 전달되 어 전도 노이즈가 발생한다.

이렇게 반향된 공진 전류는 P CB 패턴의 기생 캐패시턴스와 커플링 되어 접지를 통해서 전도 노이즈를 형성한다. 그림 3- 3 은 M OS F ET 의 전류 i(t) 와 LISN 의 50[Ω] 양단에 걸리는 전압 v (t) 를 시간축 상 에 나타낸 그림이다. 그림 3- 3 의 (a ) 는 기생 성분을 포함하지 않은 파형이고, (b ) 는 기생 성분을 포함한 파형을 나타내고 있다. 파형을 살 펴보면 스위치 턴온시에 발생되는 높은 d i/ d t 가 LISN 의 50[Ω] 에 큰 노이즈 전압으로 나타나고 있는 것을 알 수 있다.

위와 같은 현상이 일어나는 궁극적인 원인은 누설 인덕턴스에 저장되 어 있는 에너지 성분이라 할 수 있다. 따라서, 플라이백 컨버터과 같은 절연형 전원 공급기에서는 트랜스포머의 누설 인덕턴스를 최소화시킬

(a )

(b )

그림 3- 3 LISN 전압 측정

(a ) 기생 성분을 포함하지 않았을 경우의 파형 (b ) 기생 성분을 포함하였을 경우의 파형

F ig . 3 - 3 LISN V olt ag e M ea sur em en t

전체 노이즈의 두번째 주요 원인은 입력 리플 전류에 의한 성분이다.

본래 입력 캐패시터는 입력 전류의 고주파 리플 전류 성분을 제거하기 위한 목적으로 사용한다. 하지만 2 장에서 살펴보았듯이 주파수가 증가 함에 따라 자기 공진 주파수 이후에 나타나는 기생 성분 ESR 과 E SL 에 의해서 캐패시터의 효과는 감소하게 되고 E SR 에 의해서 리플 전 압이 증가하게 된다. 그러므로, 기생 성분이 적은 캐패시터, 또는 공진 주파수가 높은 캐패시터를 사용할 필요가 있다.

살펴본 바에 의하면 P CB 패턴중에서도 스위칭 동작에 관련된 패턴, 즉 M OS F ET 과 트랜스포머를 연결하는 패턴은 트랜스포머의 누설 인 덕턴스 성분과 함께 전도 노이즈를 더욱 악화시키는 성분으로 작용한다 는 것을 알 수 있다. 그러므로, 이 패턴은 가능한 짧게 구성하여 기생 인덕턴스를 최대한 줄이는 것이 요구된다. 더 나아가 2차측의 트랜스포 머와 다이오드 사이의 패턴 또한 다이오드의 역회복 특성으로 인해 누 설 인덕턴스와 패턴에 존재하는 기생 인덕턴스와 작용하여 공진 현상을 발생시키기 때문에 이 주위의 패턴 또한 짧게 구성하여 기생 성분을 줄 이는 것이 노이즈를 감소시키는 방법이 된다.

세번째 주된 노이즈 소스원은 그림 3- 4 에 보이고 있는 M OSF ET 스위치 오프시 발생되는 드레인- 소스간 전압 Vd s 의 공진 현상이다. 전 체 전도 노이즈를 분석하기 위해서는 이에 대한 정확한 분석이 우선 이 루어져야 하는데 이유는 다음과 같다.

M OSF E T 의 스위치 오프시 발생되는 공진 주파수에 해당하는 고주 파 성분은 M OSF ET 의 기생 성분인 Cd s 와 다이오드의 접합 캐패시 터, 그림 3- 5의 Cs n u b b e r 와 P CB 패턴의 기생 캐패시턴스 등의 기생 성 분들에 의해서 전도 노이즈를 발생시키고, 이것이 접지를 통해 전달되 어 전도 노이즈의 주 원인이 된다.

그림 3- 4 M OS F ET 의 Vd s 의 파형 F ig 3 - 4 M OSF ET Vd s w av eform

거듭 강조하지만 트랜스포머에는 권선에 의해서 형성되는 기생 누설 인덕턴스가 존재하게 된다. M OSF ET 의 스위치가 턴 온 되어 있는 동 안 트랜스포머에 의해서 입력 전압에 의한 에너지의 일부가 1차측에 저 장되고, M OSF ET 의 스위치 턴 오프시 트랜스포머에 저장되어 있던 에너지가 2차측으로 전달되게 된다. 이 때, 1차측에 존재하는 트랜스포 머의 누설 인덕턴스에 저장되는 에너지는 식 (3- 1) 과 같이 표현할 수 있다.

그림 3- 5 누설 인덕턴스에 의한 커플링 경로 F ig . 3- 5 Couplin g pat h of Leak a g e In du ct an ce

E = 1

2 L lI 2 (3 - 1)

스위치의 턴 오프시 누설 인덕턴스에 저장되어 있던 에너지는 순간적 으로 스너버 다이오드(1N4937)를 도통시키게 되고, 식 (3- 1) 로 표현된 누설 인덕턴스 내의 에너지는 Cs n u b b e r 를 충전시키게 된다. 이 때, 전류 의 경로를 보게 되면 그림 3- 5 에 나타낸 것 처럼 Cs n u b b e r 를 충전하려 는 방향과 M OS F ET 의 Cd s 로 흐르는 방향이 존재하게 된다.

그러나, Cd s 를 통한 전류 경로는 임피이던스가 Cs n u b b e r 를 통한 경로 보다 훨씬 크기 때문에 전류의 대부분은 Cs n u b b e r 를 통한 경로를 통해 흐르게 된다. 즉, 스너버와 누설 인덕턴스에 저장되는 에너지의 관계식 은 식 (3- 2) 로 표현된다.

WL

l + W C

sn ubber( in it ia l) = W C

sn ubber( fin a l) (3- 2)

WLl : 누설 인덕턴스에 저장되어 있던 에너지

W Csn ubber( in it ia l) : Cs n u b b e r 에 초기에 저장되어 있던 에너지

W Csn ubber( fin a l) : Cs n u b b e r 에 저장되어지는 최종 에너지

이 때, Vd s 전압은 입력 전압과 Cs n u b b e r 에 충전되는 전압이 초기 피 크치의 전압을 결정하게 된다. 피크 전압의 관계식은 식 (3- 3) 과 같이 표현된다.

Vin ita l + V = Vf in a l (3 - 3 )

1

2 L lI2 + 1

2 Csn u bbe rV2in itia l = 1

2 Csn u bbe r( Vin itial + V)2 (3 - 4 )

식 (3- 3)의 V 는 Cs n u b b e r 에서 누설 인덕턴스에 저장되어져 있던 에너지를 통해 Cs n u b b e r 에 충전되는 전압을 나타낸다. 즉, Cs n u b b e r 의 캐 패시스턴스를 통해서 Vd s 전압을 조절할 수 있다는 뜻이다.

전술된 바와 같이 패턴상에 기생 인덕턴스와 캐패시턴스가 존재하게 되면 스위치의 온/ 오프시 공진 현상이 발생한다. 이 공진의 첫 번째 피 크 전압을 스너버 회로에서 제한하지 않으면, 이 에너지로 인해 그림 3 - 4 의 파형처럼 몇 번의 공진 주기내에 감쇠되지 못하고 긴 공진 주 기를 유지하게 된다. 이렇게 여러 주기를 반복하게 되는 공진 현상은 노이즈 문제를 악화시키는 원인으로 작용하게 된다.

전도 노이즈는 스위치 전압의 dv/ d t 와 기생 캐패시터에 의해 결정

그러므로, 플라이백 컨버터에서는 전도 노이즈를 줄이기 위하여 스위 치 온/ 오프시 발생되는 고압의 dv/ d t 를 제한할 필요가 있다. 일반적으 로 트랜스포머는 신호의 공통 모드 노이즈를 제한하기 위하여 사용한다 고 알려져 있다. 그러나, 플라이백 컨버터에 사용되는 전력 전달용 트랜 스포머는 전술된 바와 같이 많은 기생 성분들로 인해 전도 노이즈의 생 성과 전달에 많은 영향을 준다. 따라서, 이들에 대한 모델링을 정확히 해야만 전도 노이즈 시뮬레이션을 실행할 수 있다.

이제까지 살펴본 결과에 의하면 절연형 플라이백 컨버터에서 주된 노 이즈 소스원은 순시적으로 변하는 1차측 전류의 d i/ d t 성분, 입력 캐패 시터의 리플 전류 성분, 주스위치의 오프시 발생하는 공진 현상 등으로 요약할 수 있다. 발생된 노이즈들은 소자 및 패턴상의 누설 성분들을 통하여 1차측으로 커플링되고 이들이 결과적인 전도 노이즈에 주된 성 분이 된다는 사실을 보였다. 다음 장에서는 시뮬레이션과 실제 플라이 백 컨버터의 제작 및 측정을 통해 제시된 이론을 검증하려 한다.

Ⅳ . 실 험 결 과 및 검 토

이전 장에서 제시되었던 기생 성분 모델링을 바탕으로 전체 노이즈 시뮬레이션을 위한 29 [W ]의 플라이백 컨버터를 설계하였다. 실제 제작 된 하드웨어 측정과 예측된 시뮬레이션 결과를 비교한다.

4 .1 플라이백 컨버터의 설계

29[W ] 플라이백 컨버터의 기본 설계 사양은 아래와 같다

4.1.1 설계 조건

- 입 력 전 원 : 85 - 220[VA C] - 출 력 전 압 : + 5 [V ] @ 1[A ]

+24 [V ] @ 1[A ] - 스위칭 주파수 : 67 [㎑]

- 최대 듀티비(Dm a x) : 0.45 - 효 율 : 80[% ]

4.1.2 트랜스포머 설계

그림 4- 2 와 같은 플라이백 컨버터에서의 트랜스포머는 스위치 턴 온시 입력 전압이 1차측 권선에 인가되며, 이 때 2차측 권선은 역방향 상태이기 때문에 2차측으로는 전류가 흐르지 않고, 인가된 에너지는 1

그림 4- 1. 29[W ] 플라이백 컨버터 회로도 F ig . 4 - 1 29[W ] F ly b ack Conv ert er Cir cu it

우선 효율과 출력 전력으로부터 입력 전력을 구하게 되면,

PIN = Pou t

= L I2peak

2 T (4 - 1)

L = V IN d t

d i (4 - 2)

식 (4- 2) 를 식 (4- 1) 에 대입하고, 또한 d i 는 Ip e a k 이고, d t 는 To n 이 된다. 그리고 수식을 정리하면, 식 (4- 3) 이 된다.

Ipeak = 2 Pou t

Vin m in Dm ax = 1 . 85A (4 - 3 )

그림 4- 2 트랜스포머 권선 구성도

F ig . 4 - 2 W in din g Con fig u r at ion of T r an sfor m er

식 (4- 3) 에서 구한 값을 다시 식 (4- 2) 식에 대입을 하게 되면 식 (4- 4 )을 이용하여 자화 인덕턴스의 값을 구했다.

L p = ( Vin m ax - 1) Dm ax Ts

Ipeak = 1 . 18 [ m H ] (4 - 4)

E I3026 의 Ae(코어의 유효 단면적)은 109[㎟] 이고, PL - 7 의 A l- V alu e 는 4000[ nH / n2]이다.

첫째, 1차 권선수를 결정하기 위하여 패러데이 법칙을 적용한 식 (4- 5 ) 를 사용한다.

NP = V IN m in Ton 108

B A e = 46 [ T ] (4- 5 )

둘째, 정상 상태 출력 전압으로부터 5[V ] 단의 권선 수를 결정한다.

N S 5 = N P ( V ou t+ V D) ( 1 - D m ax) V in m in Dm ax

= 3 [ T ] (4 - 6)

셋째, 24[V ] 단의 권선 수는 5[V ] 단에 비례하여 전압이 변화하므로 식 (4- 7) 을 적용한다.

N S 17 = ( V S 17+ VD) NS5

V S5+ VD = 10 [ T ] (4- 7 )

넷째, 요구되는 공극 길이는 식 (4- 8) 을 통해 구한다.

lg = ( 0 .4 L P I2peak) 108

A e B2max = 0 . 04 19 [ cm ] (4 - 8 )

4.1.3 입출력 캐패시터 설계

4.1.3.1 입력 캐패시터 설계

플라이백 컨버터의 입력 캐패시터를 설계하기 위해서는 우선 두 가지 를 생각해야 한다. 캐패시터에 인가할 수 있는 최대 정격 전압과 A C RM S 리플 전류다.

입력 캐패시터 선정시 주의할 것은 첫째로 과전압을 연속적으로 캐패 시터에 인가하게 되면, 누설 전류가 급격히 증가하며, 이것은 발열이나 회로 단락의 원인이 된다.

둘째로는 A C RM S 전류는 ES R 때문에 전력 소비를 일으키고, 캐패 시터 내부의 온도 상승으로 인한 수명 단축의 결정적인 원인이 된다.

먼저 과전압의 고려는, 30[% ] 마진을 고려하여 A C 입력 전압의 최대 치를 260[V ]라 할 때 260 2 1 . 3 = 478 [ WV ] 이므로 450[W V ] 캐패 시터를 사용한다.

A C RM S 전류를 계산하기 위해 입력 캐패시터의 충전 시간을 우선 구하면 식 (4- 9) 와 같다.

tc = cos - 1 ( vm in / vp k )

2 f = 2 . 11[ m s] (4 - 9)

구하게 되면, 식 (4- 10) 과 같다.

C i n =

Pou t

η td 2

( vpk2 - vm in2) = 93 [ uF ] (4 - 10)

계산된 Ci n 값과 비슷한 용량의 상용값을 구하게 되면, 100[㎌] 를 선 정할 수 있으며, 선택한 Ci n 에 대한 Vm i n 값을 구하여 A C RM S 전류 를 구한다.

tc = -

C i n ( vpk2 - v m in2) - 1 2f

1000 = cos - 1( v m in/ vpk) 2 f

(4 - 11)

식 (4- 10) 에서 A C RM S 값을 구하기 위하여 Vm in 을 구하게 되면, 90[V ] 가 된다.

[ 1 T

T / 2 T / 2 - tc

( Ci n vp k 120 cos ( 120 t ) )2d t +

T - tc

0

Po u t η vp k- vp k- vm in

td t

2

d t ]

1

2 = 1 . 0 1[ A ]

(4 - 12)

식 (4- 12) 에 의해 계산된 A C RM S 전류값을 만족하는 100[㎌] 용량 의 삼화 캐패시터를 사용한다.

4.1.3.2 출력 캐패시터 설계

출력 캐패시터 또한 입력 캐패시터와 마찬가지로 전해 캐패시터를 사 용하기 때문에 캐패시터로 흐르는 리플 전류를 정확하게 계산하여야 한 다. 그 이유는 전술된 바와 같이 리플 전류가 전해 캐패시터가 가지고

있는 ESR에 의해서 전력 손실이 발생하고, 내부 온도를 상승시키기 때 문에 캐패시터의 수명을 단축하는 원인이 된다. 본 논문에서 설계된 플 라이백 컨버터는 5[V ] 와 24[V ]의 두 가지 출력을 갖기 때문에 각각의 출력에 대해 설계한다.

1) 5 [V ] 단의 출력 캐패시터를 설계 첫째, A C RM S 전류는 다음과 같다.

I ac rm s = ( I 2P- 3 I o I P) tof f

3 T + I2o = 1 . 01A

(4- 13 ) 둘째, 캐패시터의 최대 정격 전압은 5 ×1.3 = 6.5[V ] 이다. 통상적으 로 출력 캐패시터는 100% 이상의 마진을 사용하므로 16[V ]를 사용한 다.

셋째, 캐패시터는 식 (4- 13) 의 리플 전류값를 만족하는 470[㎌]를 사 용한다.

2) 24 [V ]단의 출력 캐패시터를 설계하면,

A C RM S 전류는 식 (4 - 14) 와 같이 주어진다.

I ac rm s = ( I 2P- 3 I o IP ) tof f

3 T + I2o = 1 . 0 1[ A ] (4- 14 ) 둘째, 캐패시터의 최대 정격 전압은 24 × 1.3 = 31.2 이므로 35[V ] 를 사용한다.

셋째, 캐패시터는 식 (4- 13) 의 리플 전류값을 만족하는 1000[㎌]를

4.1.4. 반도체 소자 선정

5 [V ]단의 정류 다이오드는 최대 역방향 전압은 200[V ], 최대 전류는 7 [A ] 규격의 BY W 29- 200 를 사용한다. .

24 [V ]단의 정류 다이오드는 최대 정격 전압은 30[V ] 이고, 최대 전류 는 3[A ] 인 1N5822 을 사용한다.

입력 정류 브릿지 다이오드는 최대 정격 전압은 600[V ], 최대 정격 전류는 2[A ] 인 KBP 206G 를 사용한다.

4 .2 시뮬레이션 회로 구성

앞서 언급되었던 이론들에 의해 전도 노이즈 시뮬레이션 회로들을 구 성한다. 전도 노이즈 시뮬레이션 회로에는 수동 소자, 능동 소자, P CB 패턴상의 기생 성분들을 모두 포함한다. 이 절에서는 임피던스 분석기 를 통한 수동 소자의 모델 구성과 소프트웨어를 사용한 P CB 패턴상의 기생 성분 추출에 관한 사항들을 설명한다.

4.2.1 수동 소자 임피던스 측정 및 모델링

수동 소자 임피던스 측정은 일반적으로 사용되는 임피던스 분석기를 사용할 수 있다. 본 논문에서는 HP - 4194A 를 사용하여 임피던스를 측 정하였다.

4.2.1.1 캐패시터 측정 및 모델링

그림 4- 3 와 같이 전해 캐패시터의 임피던스 특성은 100[㎑] 미만의

그림 4- 3 입력 캐패시터 임피던스 측정 파형

F ig . 4- 3 Im p edan ce M ea su rm en t W av efor m of Input Capacit or

주파수에서 본래의 용량성 특성을 나타내지만 100[㎑] 이후로부터 1[㎒]

부근의 주파수 사이에서 E SR의 영향이 지배적이라는 사실을 알 수 있 다. 1[㎒]이상의 주파수에서는 리드에 존재하는 인덕턴스 성분이 전체 임피던스를 지배하는 성분이 된다는 사실을 알 수 있다.

각 캐패시터에 대해 임피던스를 측정하고, 측정 결과로부터 그림 2- 7 과 같은 캐패시터의 등가 회로 모델을 구성한다. 사용된 캐패시터들의 측정 결과로부터 구성되는 모델을 표 4- 1 에 나타내었다.

성분

구 분 C (㎌) E SR (Ω) E S L (H )

입력 캐패시터 95 0.5 185

출력 캐패시터

( 5 V ) 450 0.1 200 출력 캐패시터

( 24 V ) 1000 0.2 250 표 4- 1 캐패시터의 등가 회로 모델 구성

T able . 4 - 1 E quiv alen t Cir cu it M odel Con figu r ation of Capa cit or s

4.2.1.2 인덕터 측정 및 모델링

캐패시터와 마찬가지로 인덕터의 모델은 그림 2- 8 에 보이고 있는 모 델을 사용한다. 24[V ]단에 사용된 인덕터의 임피던스 측정 결과를 그림 4 - 4 에 보이고 있다. 2장에서 언급되었던 것처럼 권선 사이에 존재하는 기생 캐패시턴스로 인하여 약 45[㎒] 정도의 주파수에서 자기 공진이 발생하는 현상을 살펴볼 수 있다. 제작에 사용된 인덕터들의 모델 구성 을 표 4- 2 에 나타내었다.

성 분

구 분 L ( u H ) E SR (Ω) Cw ( ㎊ )

5 [V ]단 인덕터 3 .97 0.2 216 24 [V ]단 인덕터 4 .7 0.2 220

표 4- 2 인덕터의 등가 회로 모델 구성

T ab le . 4 - 2 E qu iv alen t Cir cu it M odel Config ur ation of In du ct or s

그림 4- 4 인덕터의 임피던스 측정 파형

F ig . 4 - 4 Im pedan ce M ea sur m en t W av eform of In du ct or

4.2.1.3 트랜스포머 측정 및 모델링

트랜스포머의 모델은 2 장에서 언급된 것처럼 [8] 에서 제시된 모델 을 사용하였다.(그림 2- 9 참조) 그림 4- 5 와 4- 6 에 트랜스포머의 측정 결과를 보이고 있다. 측정 결과로부터 구해지는 트랜스포머 모델의 매 개 변수들은 그림 4- 7 에 나타내었다. 각 매개 변수의 추출에 관한 내 용은 매우 복잡한 수식을 요구하며, 본 논문과는 관련이 없으므로 여기 서는 언급을 하지 않는다. 이에 관한 자세한 내용은 [8], [9]를 참조하기 바란다.

그림 4- 5 1차측 권선 개방 회로 측정 파형

F ig . 4 - 5 Open - Cir cu it T est W av efor m of Pr im ary W in din g s

그림 4- 6 1차측 권선 단락 회로 측정 파형

F ig . 4- 6 Sh or t - Cir cuit T est W av efor m of Pr im ar y W in din g s

그림 4- 7 트랜스포머 등가 모델 구성

F ig . 4 - 7 E qu iv alen t M odel Config ur ation of T r an sfor m er

4.2.2 PCB 패턴의 기생 성분 추출 및 모델링

2 장에서 언급된 P CB 패턴상의 기생 성분들을 손으로 계산하는 것 은 M ax w ell 방정식을 풀어야 하기 때문에 많은 시간과 계산량을 요구 한다. 현재 이러한 어려움을 극복하기 위해 P CB 의 기하학적 구조에 따라 전술된 기생 성분들을 계산하는 소프트웨어들이 소개되어 있다.

본 논문에서는 A n s oft 사의 SpiceLink 를 사용하여 P CB 패턴상의 기 생 성분들을 추출하였다. S piceLink 를 통해 P CB 를 모델링한 모습을 그림 4- 7 에 나타내고 있다. 본 논문에 사용된 플라이백 컨버터의 P CB 는 단면 기판이며, 해석시에 3D 모델링을 사용했다.

전도 잡음 모델링을 위해 모든 기생 성분을 포함한 통합 행렬 형태로 기생 성분 정보가 주어진다. 주의할 점은 본래의 모델에는 자기 캐패시 턴스가 포함되어 있지만, P CB 경로상에서 이 값은 의미가 없기 때문에 전도 잡음 시뮬레이션에는 포함시키지 않았다.

또한, 각 기생 인덕턴스간의 상호 인덕턴스는 의존 전류원의 형태로 제공되나, 그 값이 자기 인덕턴스에 비해 극히 작은 값을 나타내기 때 문에 전체 회로에 거의 영향을 주지 않으므로 이 또한 본 논문에서는 배제되었다. 최종적으로 계산된 기생 성분들을 전도 노이즈 시뮬레이션 에 사용하기 위해 SpiceLink 에서 제공하는 모델을 수정할 필요는 있 다.

그림 4- 7. SpiceLink 를 이용한 P CB 모델 F ig . 4 - 7 P CB M odel u sin g S piceLink

4 .3 실험 결과

제시된 전도 노이즈 시뮬레이션 모델의 정확성을 검증하기 위해 시뮬 레이션과 실측을 통해 노이즈의 파형을 비교・분석한다.

먼저, 시뮬레이션은 크게 세 방향으로 진행된다. 첫번째로 P CB 패턴 의 기생 성분을 포함시키지 않았을 때의 노이즈 파형, 둘째로 주 스위 칭 동작에 관련된 경로의 기생 성분만을 포함시켰을 때의 파형, 마지막 으로 전체 P CB 패턴의 기생 성분을 포함시켰을 때의 파형을 비교할 것이다. 여기서 비교된 파형을 통해서 본 논문에서는 노이즈 시뮬레이 션 시간을 단축시킬 수 있는 모델을 제시한다.

4.3.1 시뮬레이션 결과

시뮬레이션은 다음과 같이 실행된다. 먼저, 설계된 플라이백 컨버터 회 로에 그림 4- 8 과 같이 LISN 의 모델을 추가한다. 전도 잡음 측정은 LIS N 의 50[Ω] 저항에서 측정되므로, 그림에서 보여지는 Vn 1 과 Vn 2 전압으로부터 전도 노이즈를 측정한다. 언급되었던 기생 성분의 포함 유무는 플라이백 컨버터의 등가 회로를 수정함으로써 이루어진다.

기생 성분을 전혀 포함하지 않았을 경우의 회로도는 그림 4- 1 에 나 타내었고, 전도 노이즈 시뮬레이션 결과를 각각 그림 4- 9 에 나타나 있 다. 그림 4- 11 은 주요 경로의 기생 성분을 포함한 경우의 회로도와 그 림 4- 10 은 시뮬레이션 결과이다.

그림 4- 8 전도 노이즈 시뮬레이션 블럭도 F ig . 4- 8 Con du ct ed N oise S im u lation Block Diag r am

그림 4- 9 기생 성분을 포함하지 않은 전도 노이즈 스펙트럼 F ig . 4 - 9 Con du ct ed N oise Spect ru m w ith ou t P ar a sitic E lem en t s

그림 4- 10 주요 경로의 기생 성분만을 포함한 전도 노이즈 파형 F ig . 4 - 10 Con du ct ed N oise Sp ectr um w it h P ar a sitic E lem en t s of

Cr it ical P ath

그림 4- 12 전체 경로의 기생 성분을 포함한 회로도 F ig . 4 - 12 Con du ct ed n oise Sp ectr um w ith T ot al P CB Lay out

3 장에서 언급되었던 것처럼 전도 노이즈의 생성과 커플링에 가장 큰 영향을 주는 요소는 주 스위칭 경로의 기생 성분들이다. 이들 대부분은 트랜스포머를 중심으로 스위칭 전류 및 전압이 인가되는 소자들 주변에 위치해 있다. 따라서, 시뮬레이션 시간을 단축시키기 위해 주스위칭 경 로의 기생 성분들만을 포함하는 회로도를 그림 4- 11 과 같이 구성하여 시뮬레이션할 수 있다. 그림 4- 11 의 회로도를 이용한 시뮬레이션 결과 는 그림 4- 10 에 나타나 있다. 또한 전체 P CB 패턴에 대한 노이즈 결 과에 대해서도 그림 4- 12 에 나타내었다.

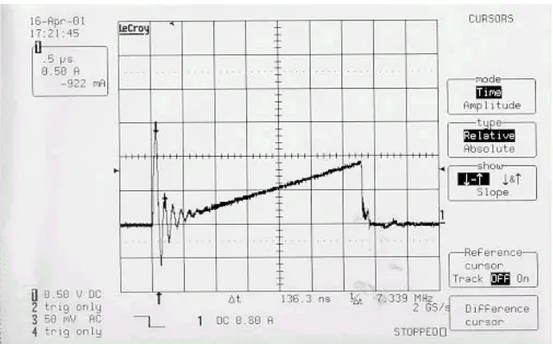

4.3.2 측정 결과

아래 그림 4- 16 는 EM CIS 사의 LISN (LN 2- 20A )과 스펙트럼 분석기

(LG - 9270A )로 측정한 하드웨어 실측 파형이다. 실측 조건은 [4]에서 제 시한 기준을 토대로 하게 된다. 자세한 내용은 그림 4- 13 과 같다.

그림 4- 13 전도 노이즈 테스트에 대한 규격 F ig . 4- 13 Lay out for Con du ct ed E m is sion N oise T est s

4 .4 결과 분석

그림 4- 9 와 그림 4- 10 에서 볼 수 있듯이 소자나 P CB 패턴 의 기 생 성분을 포함시키지 않을 시에는 정확한 노이즈 파형을 구하기가 어 려워지게 됨을 알 수 있다. 따라서 전도 노이즈에 대한 정확한 예측을 위해서는 소자가 가지고 있는 고주파에서의 기생 성분과 P CB 패턴에 대한 기생 성분을 구해서 시뮬레이션시 추가해야 함을 알 수 있다.

그림 4- 10 과 그림 4- 12를 보게 되면 P CB 패턴 전체의 기생 성분 을 포함시켜서 회로를 시뮬레이션 하는 것과 주요 경로에 대해서 해석 하는 것이 전체적인 노이즈 레벨이 10[㎒] 와 25[㎒] 대역에서 10[㏈㎶]

정도의 차이를 나타내고 있는데 이것은 주요 경로만을 넣어서 해석하는 것과 많은 차이가 나지 않을 것이라고 생각된다. 그러므로 그림 4- 11 에서 제시한 주요 경로의 기생 성분을 포함한 회로도만으로 노이즈를 예측할 수 있음을 알 수 있다.

그림4- 14 를 보게 되면 4[㎒] 와 5[㎒] 대역에서의 92[㏈㎶] 정도의 노이즈 성분은 3 장에서 설명하였듯이 M OSF ET 의 스위치 오프시 발생 되는 공진 현상에 의한 것으로 설명할 수 있다. 그만큼 공진 주파수의 노이즈 성분이 저주파수 대역에서는 큰 영향을 미치게 됨을 알 수 있 다.

그림 4- 10 과 그림 4- 14 의 노이즈 시뮬레이션 파형을 비교하게 되 면, 전도 노이즈의 레벨과 포락선이 전혀 다르게 나타나고 있지만, 4 [㎒] 와 5 [㎒] 주파수 대역에서의 노이즈 레벨이 증가되는 것과 15 [㎒]

부근에서의 노이즈 레벨이 감소하는 것과 28[㎒] 부근에서의 노이즈가 상승하는 전체적인 포락선이 그림 4- 14 와 비슷함을 알 수 있다. 그러 나 노이즈 레벨이 3[㎒]에서 6[㎒]에서는 40[㏈㎶], 18[㎒] 에서 27[㎒]에 서는 20[㏈㎶] 정도의 차이를 나타내고 있다. 이렇게 차이가 나는 것은

접지 실측 장소에서의 영전위 기준과 시뮬레이션의 영전위 기준 상황이 다르기 때문인 것으로 생각된다. 또한 노이즈를 측정하게 되면 노이즈 레벨이 시간에 따라서 조금씩 파형이 변해가고 가장 노이즈 레벨이 높 을 때의 파형을 저장하고 승인 규격을 맞추려고 한다. 따라서 시뮬레이 션을 하게 되면 시간을 정해놓은 상태에서 시뮬레이션을 하기 때문에 레벨을 맞추기가 쉽지 않은 것으로 생각된다.

그림 4- 15 주요 경로의 기생 성분의 값을 증가했을때의 파형 F ig 4 - 15 T ot al n oise w it h in cr ea sin g crit ical path elem ent s v alu e

그림 4- 15를 보면 주요 경로의 기생 성분의 값을 증가했을 때 노이 즈의 레벨이 증가함을 알수 있다. 10[㎒]에서 15[㎒]까지의 노이즈가 10[㏈㎶] 정도 증가를 했고, 25 [㎒]이상에서의 노이즈는 감소된 것처럼 보여진다. 그러므로, 노이즈를 감소시키기 위해서는 주요 경로의 기생

Ⅴ . 결 론

전원 공급기 설계 단계에서 제작 이후 발생되는 전도 노이즈에 대한 분석을 실행할 수 있는 전도 노이즈 시뮬레이션 모델을 제시하였다. 시 뮬레이션 결과 기생 성분을 포함하는 경우의 시뮬레이션은 실제 하드웨 어와 거의 유사한 형태의 전도 노이즈 특성을 보이는 것을 확인하였다.

또한, 하드웨어 측정과 시뮬레이션을 통해 P CB 패턴과 소자의 기생 성분이 전도 노이즈에 미치는 영향을 분석해 보았다. 분석 결과, 플라이 백 컨버터의 설계시 전도 노이즈에 관한 고려 사항은 다음과 같다.

플라이백 컨버터에서 전도 노이즈는 입력 캐패시터의 ES R 값과 주 스위칭 경로의 기생 성분에 의해서 많은 영향을 받는다는 것을 알 수 있었다. 이에 따라, P CB 패턴 설계시 주 스위칭 경로의 최소화, 양질의 입력 캐패시터 및 스위칭시 공진 현상을 줄이는 것이 전도 노이즈를 감 소시키는데 가장 큰 역할을 한다는 판단을 내릴 수 있다.

또한, 트랜스포머에 존재하는 누설 인덕턴스 성분에 의한 공진이 전 도 노이즈에 큰 영향력을 행사한다는 것을 알 수 있었다. 따라서, 전도 노이즈 억제를 위해서 트랜스포머 제작시에는 누설 인덕턴스를 최소화 하는 방향으로 권선을 구성해야 한다.

몇 가지 해결되지 않은 문제점으로는 전도 노이즈의 포락선은 거의 유사하지만, 레벨이 다르다는 것과 공통모드, 차동 모드 노이즈의 분리 측정에 관한 사항이 해결되지 않았다는 점이다. 따라서, 향후 과제로는 전도 노이즈의 포락선 뿐만 아니라, 레벨까지 일치하는 정확한 시뮬레 이션 모델을 연구해야 할 것이다. 또한, 공통 모드와 차동 모드 노이즈 의 분리 측정 및 시뮬레이션에 관한 연구가 병행되어야 한다. 마지막으 로 이런 예측을 통해 최적의 EM I 필터를 설계하는 연구가 진행되어야 할 것이다.

참 고 문 헌

[1] W ei Zhan g , "Int egr at ed EMI/ T herm al Design for Sw it chin g Pow er Supplies". VPE C, 1988

[2] M ax w ell Q3D Ex tr act or U ser ' s Refer en ce, An soft , 1997

[3] Ray Ridley , PWM Conv ert er T opologies, M odelin g , Contr ol an d M agn etics , 2000"

[4] T im W illiam s, "EM C for Pr oduct Design er s ", N ew n es , 1992

[5] H enry W . Ott , "N oise Redu ction T echniques in Electr onic Sy st em s ", W iley , 1987

[6] M ark I. M ontr ose, "EM C an d the Print ed Cir cuit Boar d", IEEE Pr es s, 1996

[7] LISN 매뉴얼 [8] Ridley 세미나 자료

[9] Caden ce 트랜스포머 모델링 자료

A b s t ra c t

A S tudy on th e A naly s i s for Con du cte d Emi s s ion N oi s e of F ly b ack Conv ert er

B y T a e - J in, K im

D ep ar tm en t of E lectr on ics E ng in e ering , Grad ua te S chool, K ook m in Un iv ers ity ,

S e oul, K or ea

In t his pap er , a m odelin g m eth od is pr oposed , for w hich t h e an aly sis on t h e con du ct ed - n oise of pow er supply at t h e design st ag e. A lso, som e p oint s for r edu ct ion of con du ct ed em is sion n oise ar e pr oposed su ch a s P CB lay out con fig ur at ion .

F or th is pur pose, th e g uidelin e for ex tr action of cir cu it m odels w h ich can affect con du ct ed n oise (P CB patt ern , p a s siv e an d activ e dev ices ) is pr oposed .

A ft er t h at , b a sed on th e ex tr act ed cir cu it m odel, t ot al cir cuit for con du ct ed n oise sim u lation is config ur ed . By th e sim ulation , n ois e s ou r ces an d cou plin g path s of th e fly b ack con v er t s ar e an aly zed .

F in ally , com parison b et w een sim u lat ion an d h ar dw ar e m ea sur em en t s ar e giv en . 29 [W ] fly b ack con v er t er w a s u sed for t h e v alidation of pr oposed m odel.