http://dx.doi.org/ 10.5515/KJKIEES.2012.23.11.1280 ISSN 1226-3133 (Print)

광대역 주파수 합성기용 YTO 모듈 설계 및 제작

Design and Fabrication of YTO Module for Wideband Frequency

Synthesizer

채 명 호․홍 성 용

Myeong-Ho Chae․Sung-Yong Hong 요 약

3.2~6.5 GHz 광대역 특성을 갖는 YTO(YIG Tuned Oscillator) 모듈을 설계 및 제작하였다. 위상 잡음 특성을 개선하기 위해 샘플링 믹서를 이용한 offset PLL(Phase Locked Loop) 구조로 설계하였다. 이 방식은 샘플링 믹서, 위상 비교기, 루프 필터, 전류 드라이버 회로, YTO로 구성된다. 측정 결과, 4.5 GHz에서 위상 잡음은 수식으로 도출한 값과 유사한 10 kHz offset 주파수에서 —100 dBc/Hz를 얻었다. 제작된 YTO 모듈의 위상 잡음은 동작 주파수 대역에서 기존 PLL 구조에 비해 10 dB 이상 우수함을 확인하였다.

Abstract

The 3.2~6.5 GHz wideband YTO(YIG Tuned Oscillator) module is designed, fabricated and measured. To improve the phase noise characteristic of the YTO module, offset PLL(Phase Locked Loop) structure with sampling mixer is applied. This YTO module is composed of sampling mixer, phase detector, loop filter, current driver, and YTO. The phase noise of the fabricated YTO module is measured as —100 dBc/Hz at 10 kHz offset frequency, which approxi- mates the predicted result at the center frequency of 4.5 GHz. This YTO module presents over 10 dB improved phase noise compared to conventional PLL module from operating frequency.

Key words : YTO, Wideband, Phase Noise, Offset PLL, Sampling Mixer

충남대학교 전파공학과(Department of Radio Science & Engineering, Chungnam National University)

․Manuscript received September 11, 2012 ; Revised October 25, 2012 ; Accepted November 5, 2012. (ID No. 20120911-104)

․Corresponding Author : Sung-Yong Hong (e-mail : syhong@cnu.ac.kr)

Ⅰ. 서 론

주파수 합성기는 무선통신 시스템의 송수신 회로 에서 RF를 IF로, IF를 RF로 변환하기 위한 국부 발 진기로 사용되며, 시스템의 성능에 큰 영향을 주는 핵심 부품이다[1].

본 논문의 목적은3.2~6.5 GHz의 광대역 주파수 합성기에 필요한 YTO(Yig Tuned Oscillator)를 설계 하는데 있다. YTO는 YIG(Yttrium Iron Garnet) sphere 와 Main 코일, FM 코일로 구성되고, Main 코일과

FM 코일에 흐르는 전류를 제어하여 YIG sphere에 인가되는 자장의 세기를 변화시켜 공진 주파수를 가 변하는 방식이다. YIG는 넓은 주파수 대역에서 수 백에서 수천대의 높은Q 특성을 나타내는 소자이다

[2]. 따라서 YTO는 광대역에서 Q가 매우 높아 우수 한 위상 잡음을 갖는 장점이 있지만, Main coil과 FM coil의 구조 때문에 물리적인 크기가 크며, 전류 드라 이브 회로가 필요한 단점이 있다. YTO는 보통 안정 도가 높은 기준 발진기와PLL(Phase Locked Loop)을 구성하여 사용한다. 이 경우, 출력 주파수를 기준 주

파수와 같도록 분주기를 사용하여 낮추어야 하므로, 위상 잡음이 증가하게 된다. Offset PLL 방식은 혼합 기를 이용하여 궤환되는 주파수를 낮춘 후 분주하기 때문에 분주비를 낮출 수 있어 위상 잡음을 개선할 수 있다. 또한, 위상 잡음 특성이 우수한 출력 신호 를 얻기 위해서는 기준 신호의 위상 잡음 특성이 우 수해야 한다. 주파수가 높은 기준 주파수를 구현하 기 위해 샘플링 믹서를 주로 이용한다. 샘플링 믹서 는 고조파 발생기와 혼합기가 결합된 형태로 낮은 주파수의 입력 신호가 고조파 발생기를 통해N차의 고조파를 발생시키고, RF 신호와 혼합하여 IF로 출 력하는 방식이다. 본 논문에서는 샘플링 믹서를 이 용한offset PLL 방식의 주파수 합성기 구조를 적용 하여 위상 잡음을 최소화하였다.

Ⅱ. YTO 모듈 설계

2-1 샘플링 믹서를 이용한 offset PLL

일반적인 PLL 방식은 분주한 VCO(Voltage Con- troled Oscillator)의 출력 주파수가 기준 주파수와 PFD (Phase Frequency Detector)에서 비교되고, 이에 따라 출력된 신호가 loop filter를 거쳐 VCO에 입력된다.

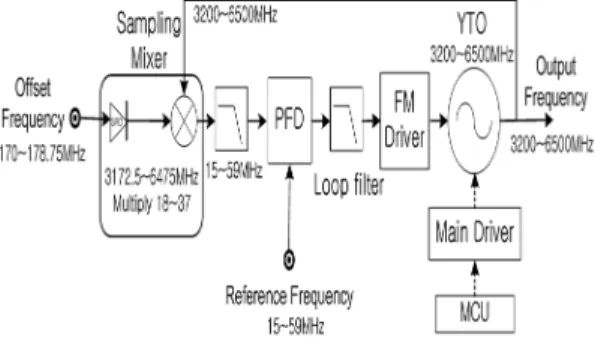

PLL의 출력 신호의 위상 잡음은 VCO의 위상 잡음, 기준 주파수의 위상 잡음, PFD의 noise floor 크기, loop filter의 대역폭에 따라 결정된다[3]. 결정된 위상 잡음은 분주비N에 따라 20logN 만큼 증가하기 때문 에PLL의 잡음 특성이 나빠지게 된다. 그림 1에 샘 플링 믹서를 이용한Offset PLL 방식을 나타내었다.

는charge pump의 이득,

는loop filter 전달함 수이며,

는VCO 전압 이득이다. 이 구조는 분주비 를 최소로 하기 위해offset 주파수를 샘플링 믹서를 이용하여 높여주고, VCO의 궤환 주파수와 혼합하여그림 1. 샘플링 믹서를 이용한 offset PLL Fig. 1 . The offset PLL using sampling mixer.

PFD에 입력한다. 샘플링 믹서에 입력된 신호는 N배 체배되기 때문에 출력 신호의 위상 잡음은 20logN 만큼 열화된다. 이 신호는 PFD에 입력되어 기준 주 파수의 위상 잡음과 PFD의 noise floor와 더해진다.

PFD 출력의 위상 잡음은 식 (1)에 의해 계산된다[4].

log

(1) 따라서 출력 주파수의 위상 잡음은 loop filter의 대역폭 내에서는 식(1)에 의해 계산된 위상 잡음 특 성이 출력되고, loop filter 대역폭 밖에서는 VCO의 위상 잡음 특성이 출력된다.2-2 YTO 모듈 구성도

본 논문에서 설계하고자 하는 YTO 모듈의 구성 도를 그림 2에 나타내었다. 샘플링 믹서를 이용한 YTO 모듈은 offset PLL 방식으로 위상 비교기와 루 프 필터, 드라이버 회로, YTO로 이루어진다. YTO의 전류는 두 개의 회로를 이용하여 제어하는 데, Main 드라이브 회로는 YTO의 큰 코일에 흐르는 전류를 제어하고, FM 드라이브 회로는 작은 코일에 흐르는 전류를 제어한다. 따라서 Main 드라이브 회로를 이 용하여 원하는 주파수 부근에서 주파수를 발생시킨 후, FM 드라이브 회로를 이용하면 원하는 주파수를 정확하게 발생할 수 있다[5]. YTO 모듈의 동작은 다 음과 같다. 먼저 MCU의 DAC의 출력 신호를 Main 드라이버로 입력한다. Main 드라이버에서는 DAC에 서 받은 신호를 전류로 변환하여 YTO로 입력하게 되고, YTO는 3.2~6.5 GHz의 대략적인 주파수를 출 력한다. 샘플링 믹서에 입력된 170~178.75 MHz인

그림 2 . YTO 모듈 구성도

Fig. 2 . Block diagram of YTO module.

offset 주파수는 내부 고조파 발생기를 이용하여 18

~37 체배되어 3,172.5~6,475 MHz의 주파수를 발생 한다.

이 신호는 샘플링 믹서 내부의 혼합기에서 YTO 의 궤환 주파수3.2~6.5 GHz와 혼합되어 15~59 MHz 의 주파수가 만들어진다. 이 신호는 저역 통과 필터를 통과한 후 위상 비교기에 입력되어 기준 주파수를 비교하여 위상차에 비례한 신호가 차지펌프를 통해 출력된다. 이 신호는 FM 드라이버 회로를 통해 전류 가 출력되어 YTO의 출력 주파수를 제어하게 된다.

본 논문에서 사용한 샘플링 믹서는 최대 주파수 가12 GHz인 Aeroflex-Metelics 사의 MSPD 1012-E50 을 사용하였고, 위상비교기는 사용 주파수 대역에서 위상 잡음 특성이 우수하며, N, R 카운터가 1이 되는 소자인 Analog Device사의 ADF-4001를 선택하였다.

YTO는 출력 주파수 대역을 만족하는 Micro Lambda 사의 MLMB-1127을 사용하였다. 그림 3과 표 1에 YTO의 구조와 규격을 나타내었다[6]. YTO는 YIG sphere에 자기 에너지를 결합하기 위해 coupling loop 를 이용한다. YTO의 coupling loop에 흐르는 전류를 조절하면YIG sphere에 인가되는 자계를 변화할 수 있고, 공진 주파수를 가변할 수 있다. Main 코일은 500에서 1,000 turn 정도로 매우 큰 코일로서 전류의 크기에 따라 자계 변화가 크다. 따라서 tuning sensi- tivity는 20 MHz/mA이다. FM 코일은 Main 코일에 비 해 정밀한 tuning이 가능하며, sensitivity는 310 kHz/

mA이다. Heat Sink는 작은 PTC(Positive Temperature Coefficient)판으로, YIG가 일정한 온도를 유지하게 하는 역할을 한다.

YTO 모듈의 경우, 샘플링 믹서를 통하여 체배와

그림 3. YTO 구조 Fig. 3 . YTO structure.

표 1. YTO 규격

Table 1. Specification of YTO.

항 목 규 격 단 위

Frequency range 3.1~6.9 MHz

Power level 14.5 dBm

Power flatness ±2 dB

Harmonics > 12 dBc

Spurious > 60 dBc

Phase noise —100@10 kHz

dBc/Hz

—123@100 kHz

Main tuning sensitivity 20±10 % MHz/mA FM tuning sensitivity 310 kHz/mA

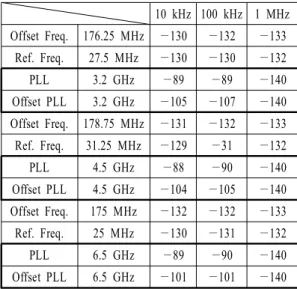

10 kHz 100 kHz 1 MHz Offset Freq. 176.25 MHz —130 —132 —133

Ref. Freq. 27.5 MHz —130 —130 —132

PLL 3.2 GHz —89 —89 —140

Offset PLL 3.2 GHz —105 —107 —140 Offset Freq. 178.75 MHz —131 —132 —133 Ref. Freq. 31.25 MHz —129 —31 —132

PLL 4.5 GHz —88 —90 —140

Offset PLL 4.5 GHz —104 —105 —140 Offset Freq. 175 MHz —132 —132 —133 Ref. Freq. 25 MHz —130 —131 —132

PLL 6.5 GHz —89 —90 —140

Offset PLL 6.5 GHz —101 —101 —140 PFD Noise Floor=—219 dBc/Hz@1Hz

Loop filter BW=150 kHz 표 2. 위상 잡음 비교

Table 2 . Comparison of the phase noise.

혼합을 하기 때문에 입력 주파수의 위상 잡음에 따 라 최종 주파수의 위상 잡음이 변화하게 된다[7],[8].

일반적인 PLL 방식과 offset PLL 방식의 위상 잡 음을 같은 조건에서 계산한 결과를 표2에 나타내었 다. 샘플링 믹서를 이용한 offset PLL 방식의 위상 잡 음이100 kHz offset 이하에서 10 dB 이상 우수함을 알 수 있다.

2-3 전류드라이버 회로 설계

YTO는 Main 코일과 FM 코일에 인가되는 전류를

그림 4. Main 전류 드라이버 회로 Fig. 4. The main current driver circuit.

제어하여 출력 주파수를 가변할 수 있다. 따라서 전 류를 제어하기 위한Main 드라이버 회로와 FM 드라 이버 회로 설계가 필요하다.

2-3-1 Main 드라이버 설계

그림 4에 YTO의 Main 전류 드라이버 회로를 나 타내었다. Main 드라이버는 제어 모듈의 DAC에서 발생되는DC 신호를 OP-AMP와 트랜지스터를 이용 해 전류를 제어한다. Main 코일의 드라이브는 MCU (Micro Controller Unit)의 DAC에서 공급하는 DC 전 압을 받아OP-AMP에서 반전 및 증폭을 하고, 전류 궤환을 받아 다시 반전한 전압으로 드라이브한다.

반전된 양의 전압은 전류 드라이브를 위한 이미터 플로워 회로를 통해 전류를 공급한다.

표1의 YTO 규격 중 Main 코일의 tuning sensitivity 가20 MHz/mA이므로 출력 주파수 3.2~6.5 GHz를 제어하기 위한 전류는160~325 mA임을 알 수 있다.

이때YTO의 저항이 약 20 Ω이므로 3.2~6.5 V 범위 의 전압이 트랜지스터의 이미터 쪽에 인가되어야 한 다. 따라서 베이스에 인가되는 전압은 적어도 3.9~

7.2 V 전압이 되어야 한다. DAC에서 출력되는 전압 의 범위는0~2.5 V이며, 이 전압은 반전 증폭기 두 개를 거쳐 베이스 인가 전압인3.9~7.2 V가 나와야 한다. 이를 위해 첫 번째와 두 번째 반전 증폭기의 이 득을 조절하였다. 첫 번째 반전 증폭기에서는 R2의 저항 값을47 kΩ으로 정하여 약 4.7배 증폭을 하여

그림 5. FM 전류 드라이버 회로 Fig. 5 . The FM current driver circuit.

0~12 V의 전압을 얻었다. 중앙의 저항단 R4는 3.3 V의 가변 전압 범위를 출력하기 위해 6.2 kΩ으로 하였다. R3는 5 kΩ의 가변 저항과 6.2 kΩ을 직렬 연결하여 전류를 조절할 수 있게 하였다. 두 번째 반 전 증폭기에서는R5의 저항 값을 2.7 kΩ으로 정하 여 3.9~7.2 V 사이의 전압을 출력하게 하였다.

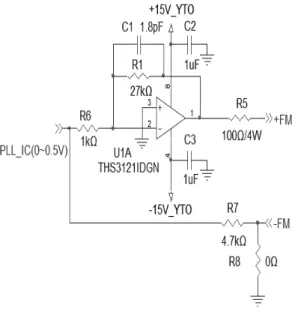

2-3-2 FM 드라이버 설계

그림5에 YTO의 FM 전류 드라이버 회로를 나타 내었다. FM 코일은 PLL IC의 Charge pump의 출력 전압으로 제어한다. 출력된 전압은 양의 전압으로 전류 궤환을 받게 되고, 출력된 전압과 궤환 전압이 합해져OP-AMP에 입력되고, 출력 전류에 의해 FM 코일을 제어한다.

표1의 YTO 규격 중 FM tuning sensitivity가 310 kHz/mA이므로 30 MHz 이상의 주파수 조정 범위를 얻기 위해서는0~116 mA의 전류 제어가 필요하다.

이를 위해 반전 증폭기를 이용하여 PLL IC에서 나 온 신호를 0~12.5 V 범위의 전압으로 출력시키기 위해 R2를 22 kΩ으로 정하였다.

YTO의 드라이버 회로를 구동할 때 Main, FM 드 라이버의 OP-AMP 뒷단의 저항, 그리고 Main 드라 이버의 트랜지스터는 최대 325 mA의 높은 전류가 흐르기 때문에 많은 열이 발생한다. 따라서 높은 열

그림 6. 루프 필터 Fig. 6 . Loop filter.

에도 저항 값이 변하지 않고, 정격전력이 높은 저항 을 사용하였다.

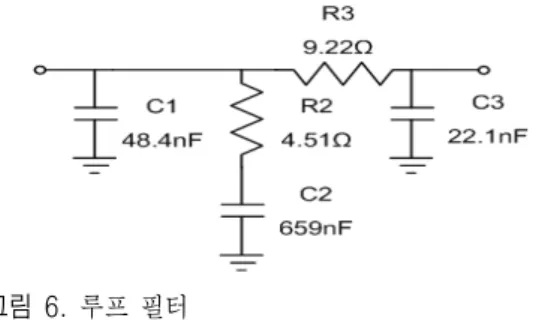

2-4 루프 필터 설계

최적의 위상 잡음 특성을 가지도록 설계하기 위 하여open loop 대역폭에 따른 고주파의 불요주파수 억제 특성이 좋은Type Ⅱ 4차 루프 필터를 설계하 였다. 그림 6에 나타낸 루프 필터는 1개의 zero와 3 개의 pole로 이루어지며, 저역 통과 필터에 의한 채 널 주파수에서의 감쇠를 식 (2)에 나타내었다[9].

log

(2)식(2)에서 AT는 감쇠량,

는 시정수이다. log 앞 계수가 20인 이유는

에서의 감쇠가 추가적인 필 터 앞단의 필터의 영향도 포함하기 때문이다. 식 (3) 에 루프 필터의open loop 이득을 나타내었다[10].

sec

tan

(3) L(s)는 루프 필터의 open loop gain,

는charge pump의 이득,

는VCO의 전압 이득이다. 식 (3)으 로부터 위상이득

를 구하면 다음과 같다. tan

tan

tan

tan

tan

(4) 식 (4)를 미분하여

≪

1이라고 가정하면, open loop 대역폭

는 식 (5)와 같이 쓸 수 있다.

tan

tan

(5) Open loop 대역폭

, 위상이득

, 채널 간격 에서의 감쇠AT의 값을 설정하면 루프 필터의 정수 값을 식 (6)~(10)을 이용해 계산할 수 있다[11].

(6)

(7)

(8)

(9)

(10) 위 식을 이용하여 차단 주파수가150 kHz, 위상마 진이 45°인 설정하여 루프 필터를 설계하였다.

Ⅲ. 제작 및 측정

3-1 제작

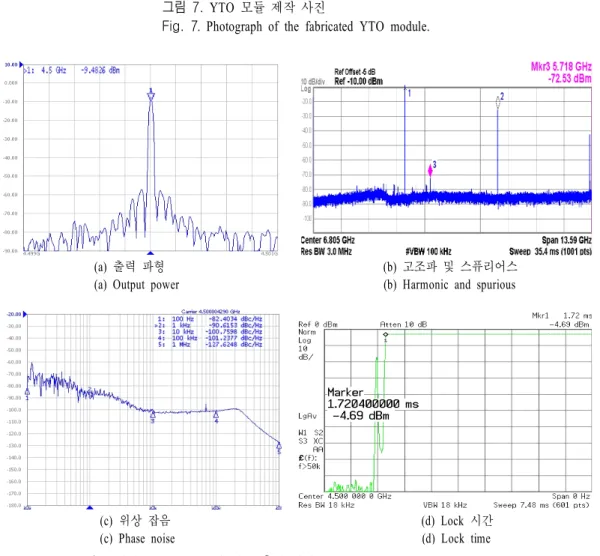

설계된 YTO 모듈을 제작하였다. 유전율이 4.7인 FR4 기판을 사용하여 4층으로 제작하였으며, 크기 는12.7 cm×10.5 cm이다. 드라이버 회로와 YTO, 레 귤레이터 등은 열을 많이 발생하므로, 방열을 위해 스크루를 이용하여 케이스에 밀착하였다. 또한, 각 전원을 기능 별로 분류하고, GND 또한 분리하여 스 퓨리어스 발생을 최소화 하였다. YTO 모듈의 제작 사진을 그림 7에 나타내었다.

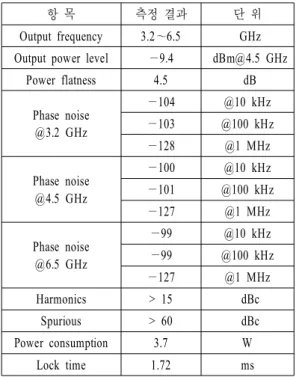

3-2 측정 결과

제작된 YTO 모듈의 4.5 GHz의 출력 특성을 Agilent 사의 신호원 분석기(E5052A)로 출력 파형과 위상 잡음을, 스펙트럼 분석기(E4445A)로 스퓨리어 스와 lock 시간을 측정하여 그림 8에 나타내었다.

표4에 제작된 YTO 모듈의 전체 특성을 요약하였

(a) 상면부 (b) 하면부

(a) Top view (b) Bottom view 그림 7. YTO 모듈 제작 사진

Fig. 7 . Photograph of the fabricated YTO module.

(a) 출력 파형 (b) 고조파 및 스퓨리어스

(a) Output power (b) Harmonic and spurious

(c) 위상 잡음 (d) Lock 시간 (c) Phase noise (d) Lock time 그림 8 제작된 YTO 모듈의 성능 측정 결과

Fig. 8. Measured results of the performance of the fabricated YTO module.

다. 출력 주파수 3.2~6.5 GHz에서 위상 잡음은 설계 규격을 대부분 만족하였다. 하모닉 주파수는 —15

dBc 이하, 스퓨리어스 특성은 —60 dBc 이하로 측정 되었다. 출력 전력은 4.5 GHz에서 —9.4 dBm, 전력

항 목 측정 결과 단 위 Output frequency 3.2~6.5 GHz Output power level —9.4 dBm@4.5 GHz

Power flatness 4.5 dB

Phase noise

@3.2 GHz

—104 @10 kHz

—103 @100 kHz

—128 @1 MHz

Phase noise

@4.5 GHz

—100 @10 kHz

—101 @100 kHz

—127 @1 MHz

Phase noise

@6.5 GHz

—99 @10 kHz

—99 @100 kHz

—127 @1 MHz

Harmonics > 15 dBc Spurious > 60 dBc

Power consumption 3.7 W

Lock time 1.72 ms

표 3. YTO 모듈 측정 결과

Table 3 . Measured data of YTO module.

평탄도는 약4.5 dB 이하로 측정되었다. Lock 시간은 1.72 ms로 측정되었고, 이는 일반적인 PLL 방식과 거의 유사함을 확인하였다.

표4에서 알 수 있듯이 대부분 설계규격을 만족하 나, 1 MHz offset 주파수에서 위상 잡음을 만족하지 않음을 알 수 있다. 이는 loop filter의 감쇠 특성이 100 kHz에서 1 MHz로 갈 때 위상 잡음 감쇠가 —25 dBc/Hz이므로 100 kHz에서는 —103 dBc/Hz, 1 MHz 에서는 —128 dBc/Hz의 위상 잡음이 나타난 것이다.

따라서 위상 잡음이 좀 더 낮은 신호를offset 주파수 로 입력한다면, 전체적인 위상 잡음이 낮아져 1 MHz offset에서 위상 잡음을 만족하리라 예상된다.

Ⅳ. 결 론

본 논문에서는 YTO를 이용하여 광대역 주파수 합성기용YTO 모듈을 설계 및 제작하였다. YTO 모 듈은 샘플링 믹서와offset PLL 방식을 이용하여 저 위상 잡음을 얻도록 설계하였다. 또한, YTO를 안정 적으로 구동하기 위한 전류 드라이버 회로와 루프필 터를 설계하였다. YTO를 위한 드라이버 단은 비교

적 전류가 많이 흐르기 때문에 온도에 영향을 받지 않고 높은 전류를 낼 수 있는 소자로 구성하였다. 메 인 드라이버 회로는C8051의 DAC의 전압을 이용하 여OP-AMP와 트랜지스터를 거쳐 YTO의 메인 코일 에 인가되는 전류의 크기를 결정하였다. 같은 방법 으로YTO FM 코일 제어에 필요한 전류가 나오도록 FM 드라이버를 설계하였다. 제작된 YTO 모듈의 기 준주파수와offset 주파수를 신호발생기를 이용하여 입력한 후 출력 주파수 특성을 측정하였다. YTO 모 듈의 위상 잡음은3.2 GHz에서 6.5 GHz의 동작주파 수 범위에서 설계 결과와 거의 일치함을 확인하였 다. 4.5 GHz에서 위상 잡음은 수식으로 도출한 값과 유사한10 kHz offset 주파수에서 —100 dBc/Hz를 얻 었다. 이 결과로부터 기존 PLL 구조에 비해 10 dB 이상 우수함을 확인하였다. 또한, 고조파 및 스퓨리 어스 특성도 설계 규격에 만족하였다.

따라서 제작된 YTO 모듈은 향후 광대역 주파수 합성기 제작에 사용 가능하다고 판단된다.

참 고 문 헌

[1] 이형구, "100~1,000 MHz 대역 초고속 주파수 합성기 설계 및 제작", 충남대학교 석사학위논 문, 2010년.

[2] 이문규, 염경환, 남상욱, "YIG 공진기를 이용한 고주파 광대역 발진기 설계 및 제작", 한국전자 파학회논문지, 19(9), pp. 1710-1718, 1994년 9월.

[3] 김영완, 박동철, "위성통신 시스템용 위상 고정 루프 주파수 합성기의 위상 잡음 예측 모델", 한 국전자파학회논문지, 14(8), pp. 777-786, 2003년 8월.

[4] 임주현, 송성찬, "DAC를 이용한 Offset-PLL 설계 및 제작", 한국전자파학회논문지, 22(2), pp. 258- 264, 2011년 2월.

[5] 이창훈, 김광동, 김효령, 정문희, 한석태, 제도흥, 김태성, "YIG 발진기를 이용한 100 GHz 대역 국 부발진 시스템 설계 연구", J. Astron. Space Sci., 20(3), pp. 185-196, 2003년.

[6] Dave Castetter, An Introduction to YIG Tuned Os- cillators, MicroSource Inc.

[7] 김정목, 임종수, 전중창, 김태수, 안광호, 이승학,

"YIG-VCO를 사용한 산업용 마이크로파 거리계 의 개발", 한국전자파학회논문지, 11(1), pp. 18- 25, 2000년 1월.

[8] 이창훈, 정문희, 김광동, 김효령, "YIG VCO를 이 용한 밀리미터파 수신기의PLL 시스템 연구", 전 자공학회 논문지, 42(11), pp. 45-52, 2005년 11월.

[9] Roland E. BEST, Phase-Locked Loops, McGraw- Hill, 2003.

[10] 류준규, "IMT-2000용 Fractional-N PLL 모듈 설 계 및 제작", 충남대학교 석사학위논문, 2001년.

[11] 고윤수, "WLL용 PLL 모듈 설계 및 제작", 충남 대학교 박사학위논문, 1999년.

채 명 호

2012년 2월: 충남대학교 전파공학 과 (공학사)

2012년 3월~현재: 충남대학교 전파 공학과 석사과정

[주 관심분야] 주파수 합성기, RA- DAR 시스템

홍 성 용