저작자표시-비영리-변경금지 2.0 대한민국 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게 l 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다. 다음과 같은 조건을 따라야 합니다: l 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다. l 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다. 저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다. 이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다. Disclaimer 저작자표시. 귀하는 원저작자를 표시하여야 합니다. 비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다. 변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

碩士學位論文

3-레벨 NPC 인버터의

중성점

전압 평형 유지를 위한

간단한

공간벡터 PWM 기법

A Simple Space Vector PWM Scheme for

Neutral Point Voltage Balance of

Three-Level Neutral Point Clamped Inverter

高

崙 赫

漢陽大學校

大學院

碩士學位論文

3-레벨 NPC 인버터의

중성점

전압 평형 유지를 위한

간단한

공간벡터 PWM 기법

指導敎授

玄 東 石

이

論文을 工學碩士學位 論文으로 提出합니다.

2014年 6月 14日

漢陽大學校

大學院

電

氣 工 學 科

高

崙 赫

i

목

록

목 록 ··· i 표 목 록 ··· ii 그림목록 ··· ii 국문 요지 ··· iii 제 1 장 서론 ··· 1 1.1 연구 배경 및 필요성 ··· 1 1.2 기존 연구에 대한 고찰 ··· 2 1.3 연구 내용 및 구성 ··· 3 제 2 장 3-레벨 NPC 인버터의 특성 ··· 4 2.1 3-레벨 NPC 인버터의 구성 및 스위칭 상태 ··· 4 2.2 3-레벨 NPC 인버터의 DC-Link 중성점 전압 변동··· 6 제 3 장 통합 전압 변조에 의한 SVPWM ··· 8 3.1 통합 전압 변조에 의한 SVPWM ··· 8 제 4 장 제안된 중성점 전압 제어 기법 ··· 12 4.1 제안된 중성점 전압 제어 원리 ··· 12 4.2 제안된 중성점 전압 제어 구현 ··· 15 제 5 장 시뮬레이션 및 실험 결과 ··· 19 5.1 시뮬레이션 ··· 19 5.2 실험 결과 및 검토 ··· 24 제 6 장 결론 ··· 33 참고 문헌 ··· 35ii

표

목 록

표 2.1 3-레벨 NPC 인버터의 스위칭 상태와 폴 전압 ··· 4 표 2.2 크기에 따른 전압벡터의 분류 ··· 5 표 4.1 DC-Link 상단 및 하단 커패시터의 충/방전 효과 ··· 12 표 5.1 유 도 전 동 기 의 정 격 과 파 라 미 터 · · · 2 5그

림 목 록

그림 2.1 3-레벨 NPC 인버터 토폴로지 ··· 4 그림 2.2 3-레벨 인버터의 공간전압 벡터도 ··· 5 그림 2.3 DC-Link 커패시터와 부하상태에 따른 중성점 전압변동 ··· 7 그림 3.1 통합된 PWM ··· 9 그림 3.2 가능한 오프셋 시간의 도표(변조지수: 0.9) ··· 10 그림 4.1 DC-Link 상단 및 하단 커패시터의 충/방전 효과 ··· 13 그림 4.2 Voffset_comp 주입과 전압 벡터 인가시간 Ⅰ··· 16 그림 4.3 Voffs et_comp 주입과 전압 벡터 인가시간 Ⅱ···17 그림 4.4 제어 블록 다이어그램··· 18 그림 5.1 3-레벨 NPC 인버터의 시뮬레이션 모델 ···· ·· · ·· ·· ·· ·· ·· ·· ·· ·· ·· ·· · ·· ·· ·· ·· ·· ·· · 19 그림 5.2 중성점 전압 제어를 고려하지 않은 시뮬레이션 결과 ··· 21 그림 5.3 PI 제어기 유/무에 따른 중성점 전압 변동 시뮬레이션 결과(DC-Link전압 및 제안된 offset) ··· 22 그림 5.4 PI 제어기 유/무에 따른 중성점 전압 변동 시뮬레이션 결과(DC-Link전압 및 선간전압) ··· 23 그림 5.5 3-레벨 NPC 인버터 실험 세트 ··· 25 그림 5.6 불평형 오프셋 인가 후 상/하단 커패시터 전압 및 출력 선간 전압 ··· 26 그림 5.7 제안한 공간벡터 PWM 기법을 적용한 무부하 40Hz 실험결과 ··· 26 그림 5.8 제안한 공간벡터 PWM 기법의 실험결과 (무부하, 40Hz) ··· 27 그림 5.9 제안한 공간벡터 PWM 기법을 적용한 무부하 50Hz 실험결과··· 28 그림 5.10 제안한 공간벡터 PWM 기법의 실험결과 (무부하, 50Hz) ··· 29 그림 5.11 제안한 공간벡터 PWM 기법을 적용한 무부하 50Hz 실험결과··· 30 그림 5.12 제안한 공간벡터 PWM 기법의 실험결과 (무부하, 50Hz) ··· 31 그림 5.13 제안한 공간벡터 PWM 기법을 적용한 부하 60Hz 실험결과··· 32iii

국문요지

3-레벨 중성점 다이오드 클램프(NPC) 멀티레벨 인버터는 우수한 토폴로지로 알려져 있다. 하지만 중성점 전압이 변동한다는 문제가 내재하고 있다. 본 논문에서는 3-레벨 NPC 인버터의 중성점 전압을 제어하기 위해 전압변조 기술을 활용한 간단한 제어 기법이 제안하였다. 제안된 설계(Scheme)는 중성점 전압의 변동을 제어하는 요소를 포함하는 계산된 오프셋(Offset) 전압을 이용하여 중성점 전압을 제어한다. 중성점 전압의 변동은 추가적인 노력 없이 간단히 보상되며, 통합 전압 변조에 쉽게 적용된다. 제안된 설계의 유효함은 시뮬레이션과 실험 결과를 통해 검증하였다.1

제

1 장 서 론

1.1 연구 배경 및 필요성

3-레벨을 포함한 멀티-레벨 인버터 기술은 본래 단일 전력용 반도체 소자를 사용한 기존 2-레벨 인버터 전력회로의 용량 한계를 극복하기 위한 응용 기술로 주로 적용되어 왔다. 최근에는 전력 수요에 대한 증가 및 화석에너지 고갈 등에 따른 에너지 효율 향상에 대한 관심의 증대와 더불어 기존 인버터 시스템보다 향상된 전력변환 효율의 구현이 가능하다는 기술적 장점이 부각되면서 적용분화가 다양화 되고 있다. 같은 입력 전압 정격을 갖는 2-레벨 인버터와 비교해서 3-레벨 인버터는 다음과 같은 장점을 지닌다. - 낮은 전압 정격을 가지는 스위칭 소자의 사용으로 효율적인 회로 설계가 가능하다. 주 스위칭 소자의 전압 정격이 낮아짐에 따라 인버터 운전 시 발생하는 도통 손실 및 스위칭 손실이 저감되며, 이를 통해 향상된 전력변환 효율의 구현이 가능하다. 전력 변환 효율의 향상을 통해 인버터 시스템의 고밀도화, 소형화에 유리하다. - 출력 전압의 레벨이 증가할수록 스위칭 과도상태 동안에 발생하는 dV/dt와 surge 전압의 크기가 비례적으로 감소한다. - 멀티-레벨 인버터는 레벨 증가에 따라 동일한 스위칭 주파수에서 양호한 출력 고조파 특성을 얻을 수 있다. 1981년 인버터 출력 전압의 고조파를 감소시키기 위한 목적의 3-레벨 NPC 인버터가 제안된 후 다양한 형태의 응용회로가 개발되었으며 이 외에도 H-bridge 인버터, 플라잉 커패시터(flying capacitor) 인버터가 산업 현장에 적용되고 있다.2

1.2 기존 연구에 대한 고찰

3-레벨 중성점 다이오드 클램프(NPC) 인버터는 중, 대전력 산업 분야에 폭넓게 사용되고 있다. NPC 인버터의 출력 파형은 2-레벨 인버터와 비교했을 때 같은 스위칭 주파수에서 적은 하모닉(harmonic) 왜란을 발생하기 때문에 3-레벨 NPC 인버터는 최근에 저전압 드라이브 구동에 사용 되고 있다. 그러나 3-레벨 NPC 토폴로지는 DC-Link 중성점 변동과 불평형 문제가 내재하고 있어 DC-DC-Link 중성점 전압 평형을 위해 제어가 필요하다[1]. 위와 같은 문제들을 해결하기 위해 DC-Link 중성점 전압 제어에 관한 많은 연구가 진행 되어지고 있다[2]-[10]. DC-Link 중성점 전압을 제어하기 위해 중성점 전압에 기준 신호를 더해 주는 수정된 SPWM 전압 벡터를 선택하는 방법이 제안되었고 DC-Link 중성점 전압 평형 유지에 대한 검증을 보여주고 있다[3]. 그리고 DC-DC-Link 커패시터 설계 및 분석을 통해 DC-Link 중성점 전압의 평형 유지와 안정성을 위한폐루프(closed loop) 제어 방법이 제안되기도 하였다[4]. DC-Link 중성점 전압의 평형

유지와 스위칭 손실을 줄이기 위해서 영전압 스위칭 방법을 제안하기도 하였다[5]. 더 나아가 중복(redundancy) 전압 벡터에 관한 방법을 연구하는 논문도 있다[6]. 이 방법은 DC-Link 중성점 전압변동에 영향을 주고, DC-Link 중성점 전압 평형 유지를 효율적으로 제어하는 벡터를 선택하는 것이다. 그러나 복잡한 과정의 시간계산과 중복 벡터의 조합과 같은 문제가 있다. 또한 인버터 출력전압 전 범위에 걸친 DC-Link 중성점 전압과 부하 역률을 제어하기 위해 가상공간 벡터 개념을 도입한 연구도 있다[7]. 이 개념은 DC-Link 중성점 전압을 제어하기 위한 유효전압 벡터를 선택한다. 기존의 3-레벨 NPC 인버터의 DC-Link 중성점 전압 평형을 위한 기술의 한 가지 결점은 저 주파수에서 DC-Link 중성점 전압 진동을 나타낸다는 것이다[8]. 이러한 전압 진동은 스위칭 소자에 전압 스트레스를 가중시켜 스위칭 소자가 견딜 수 있는 특정 전압을 초과하게 될 경우 시스템 전체에 악영향을 미치게 된다. 저 주파수에서의 3-레벨 NPC 인버터의 DC-Link 전압 진동을 제거하기 위해서 몇몇의 변조 기술이 제안되고 있다[8], [9]. 그러나 이러한 설계는 DC-Link 중성점 전압의 평형 유지를 위해 추가적인 제어 루프가 요구된다.

3

1.3 연구 내용 및 구성

본 논문에서는 상기의 문제점을 개선하기 위해 3-레벨 NPC 인버터에 대한 중성점 전압 제어가 이뤄진 간단한 공간 벡터 PWM 기법을 제안하였다. 제안된 기법은 통합된 전압 변조 기술[10]을 기반으로 하는 중성점 전압 제어 요소를 포함하는 오프셋 전압을 계산한다. 중성점 전압 제어 요소는 전압 변조를 단순화 하는 것으로 정의되고, 통합된 전압 변조 기술을 이용하여 공간벡터 PWM 설계에 용이하게 적용된다. 제안된 중성점 전압 제어 기법은 시뮬레이션과 실험을 통해 검증하였다. 본 논문은 제 1 장의 서론을 포함하여 6의 장으로 구성하였다. 제 2 장은 3-레벨 NPC 인버터의 구성 및 스위칭 상태 그리고 3-레벨 NPC 인버터의 DC-Link 중성점 전압 변동 문제에 대해 기술한다. 제 3 장에서는 통합 전압 변조에 의한 SVPWM 기법에 대해 설명한다. 제 4 장에서는 제안된 중성점 전압 제어 설계에 대해 기술하였다. 제 5장은 시뮬레이션 및 실험 결과를 제시하고 제안한 기법의 타당성을 검증한다. 마지막으로, 제6장에서는 결론을 기술한다.4

제

2 장 3-레벨 NPC 인버터의 특성

2.1

3-레벨 NPC 인버터의 구성 및 스위칭 상태

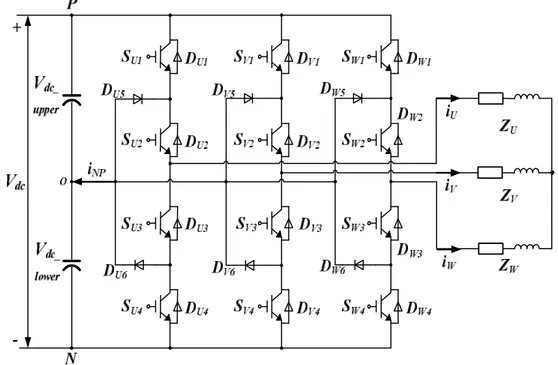

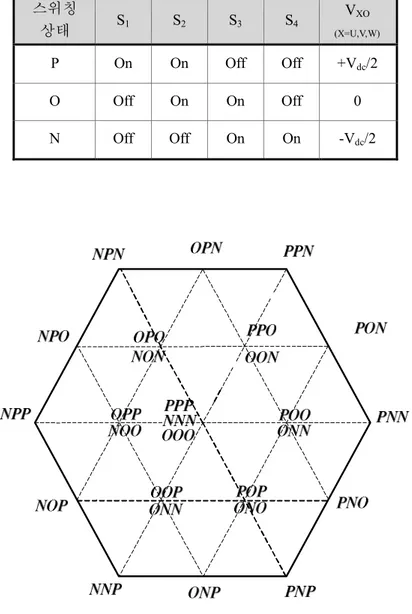

그림 2. 1은 3-레벨 NPC 인버터의 토폴로지를 나타내고 있다. 3-레벨의 출력전압 특성을 구현하기 위해서 각 인버터 레그는 4개의 스위칭 소자와 4개의 역병렬 다이오드, 그리고 2개의 클램핑 다이오드로 구성되어 있다. 클램핑 다이오드는 DC-Link 커패시터의 중성점과 연결되어 있으며 0 전압에 클램핑 시키는 작용을 한다. 3-레벨 NPC 인버터는 각 상마다 P, O 그리고 N 상태의 3가지 스위칭 상태를 갖는데 표 2. 1에 각 스위칭 상태 및 출력 폴 전압을 나타냈다. 각 상마다 3가지의 스위칭 상태를 갖기 때문에 3상을 조합하였을 경우 총 27개의 스위칭 상태를 갖게 되며, 이를 공간벡터도 상에 나타내었을 때는 그림 2. 2와 같다. 또한 공간벡터도 상의 모든 전압 벡터는 출력 상전압의 크기에 따라 표 2. 2와 같이 분류할 수 있다. 그림 2. 1 3-레벨 NPC 인버터 토폴로지5

표 2. 1 3-레벨 NPC 인버터의 스위칭 상태와 폴 전압

Table 2. 1 The switching state and pole voltage for a three-level NPC inverter 스위칭 상태 S1 S2 S3 S4 VXO (X=U,V,W) P On On Off Off +Vdc/2 O Off On On Off 0 N Off Off On On -Vdc/2 그림 2. 2 3-레벨 인버터의 공간전압 벡터도

Fig. 2. 2 Space vector diagram of a three-level inverter

큰 벡터(Large Vector)는 1상 또는 2상이 +Vdc/2에 연결되고 다른 상은 –Vdc/2에 연

결된 경우로 6가지의 스위칭 조합이 존재하게 된다. 중간 벡터(Middle Vector)는 큰 벡 터 보다는 작고 중복 벡터(Redundancy Vector) 혹은 작은 벡터(Small Vector)보다는 큰

6

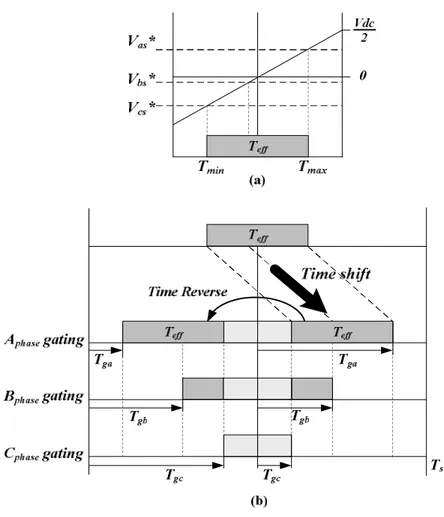

표 2. 2 크기에 따른 전압벡터의 분류

Table 2. 2 Classification of the output voltage vector according to the magnitude

전압벡터의 분류 스위칭 상태

큰 벡터

(Large Vector) (PNN),( PPN), (NPN), (NPP), (NNP), (PNP)

중간 벡터

(Middle Vector) (PON), (OPN), (NPO), (NOP), (ONP), (PNO)

중복 벡터

(Redundancy Vector)

(POO), (PPO), (OPO), (OPP), (OOP), (POP) (ONN), (OON), (NON), (NOO), (NNO), (ONO)

영 벡터

(Zero Vector) (NNN), (OOO), (PPP)

가지의 스위칭이 존재하며, 마지막으로 부하로 전력 공급이 이루어지지 않는 3가지의 영 벡터(Zero Vector)가 존재한다.

2.2

3-레벨 NPC 인버터의 DC-Link 중성점 전압 변동

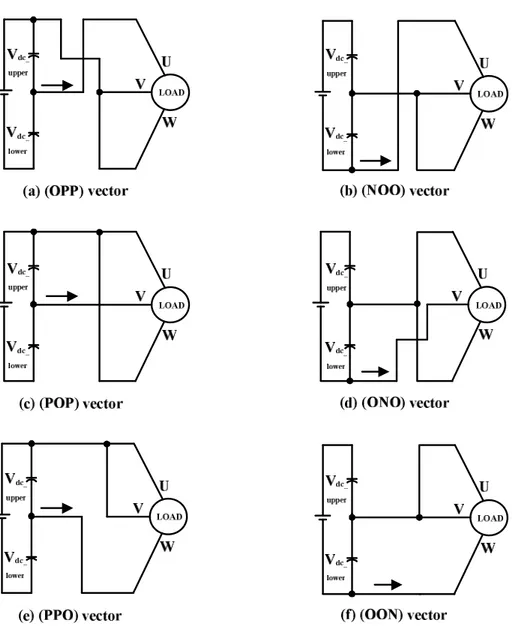

3-레벨 NPC 인버터는 입력 전압원 역할을 하는 DC-Link 커패시터가 상단 커패시터 와 하단 커패시터가 직렬 연결된 구조로 되어 있다. 각각의 전압은 Vdc/2로 가정하지 만 실제로는 각 전압벡터의 스위칭 상태에 따라 상단 및 하단 커패시터의 전압은 영 향을 받게 된다. 큰 벡터와 영 벡터는 DC-Link 중성점 전압 변동에 영향을 미치지 않 지만 중복 벡터와 작은 벡터는 DC-Link 중성점 전압 변동에 영향을 미친다. 하지만 실제로 상/하단 커패시터의 충/방전을 결정하는 것은 중복 벡터와 작은 벡터가 선택 되었을 때의 전류의 방향이다. 전류에 따라 DC-Link 중성점 전압이 변동하는 경우를 그림 2. 3에 나타내었다. 그림 2. 3(a), (c), (e)는 상단 커패시터가 충전되는 경우로 DC -Link 중성점 전압이 하강하는 경우를 나타내고 있으며, 그림 2. 3(b), (d), (f)는 하단 커패시터가 충전되어 중성점 전압이 상승하는 경우를 나타내고 있다.7

(a) 중성점 전압 하강 (b) 중성점 전압 상승

(c) 중성점 전압 하강 (d) 중성점 전압 상승

(e) 중성점 전압 하강 (f) 중성점 전압 상승 그림 2. 3 DC-Link 커패시터와 부하상태에 따른 중성점 전압변동 Fig. 2. 3 Neutral voltage fluctuation by the DC-Link capacitors and load connection

8

제

3 장 통합 전압 변조에 의한 SVPWM

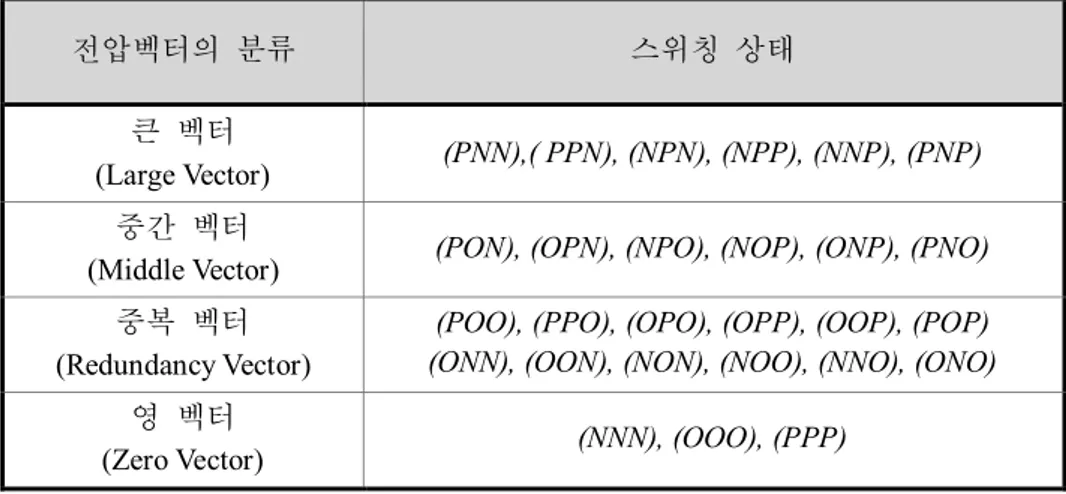

3.1 통합 전압 변조에 의한 SVPWM

기준 상전압(phase reference voltage)을 이용하면, 섹터를 판별하고 다시 조합하는 번

거로움 없이 직접 스위칭 시간을 구할 수 있다. 즉, 유효벡터(effect vector)가 인가되는 시간과 기준 상전압과의 관계를 고려하여 스위칭 시간을 구할 수 있다. 즉, 유효벡터 가 인가되는 시간과 기준 상전압과의 관계를 고려하여 스위칭 시간을 구할 수 있다. 그림 3. 1 (a)에 보여주듯이, 다른 시기에 한 샘플링 기간 동안 각 상의 스위칭 상태가 1에서 0으로 바뀔 때, 유효전압은 부하측에 적용된다. Ts는 샘플링 시간을 의미하며, Teffect는 다른 전압이 유지되는 지속 시간을 의미한다. 이 값은 상 전압과 직접적인 관 련이 있고, 비례 형성은 다음과 같이 정의할 수 있다. * * * * * *

:

:

:

:

:

:

cs dc s cs s cs dc cs bs dc s bs s bs dc bs as dc s as s as dc asV

V

T

T

T

T

V

V

V

V

T

T

T

T

V

V

V

V

T

T

T

T

V

V

×

º

Þ

=

×

º

Þ

=

×

º

Þ

=

(3.1) 기준 상전압을 이용하면, 섹터를 판별하고 다시 조합하는 번거로움 없이 직접 스위칭 시간을 구할 수 있다. 이때 상전압의 상태가 전이하는 시간 Tas, Tbs, Tcs는 일정 주기에 대한 DC-Link 전압 과 기준상전압의 비율로 정의된다. 공간 벡터 PWM에서 유효벡터가 인가되는 시간은 선간전압이 인가되는 시간이다.Tmax와 Tmin 사이의 전압이 "유효시간(effective time)"이며 Teff로 정의 된다.

min max

T

T

9

그림 3. 1 통합된 PWM : (a) 유효시간과 출력 전압의 관계

(b) 실제 게이팅 시간 발생

Fig. 3. 1 Unified PWM : (a) Relationship between the effective time and the output voltage (b) Actual gating time generation

시간 지연 동작은 각각의 인버터 레그(leg)에 대한 실제 게이팅 시간 (Tga, Tgb, Tgc)을 생성하기 위해 가상의 스위칭 시간이 적용된다. 이를 그림 3. 1 (b)에 나타내고 있다. 실제 스위칭 시간은 가상 스위칭 시간에 특정 편차(Toffset)를 더함으로써 다음과 같다: offset cs gc offset bs gb offset as ga

T

T

T

T

T

T

T

T

T

+

=

+

=

+

=

(3.3)10

p

q

p 2p

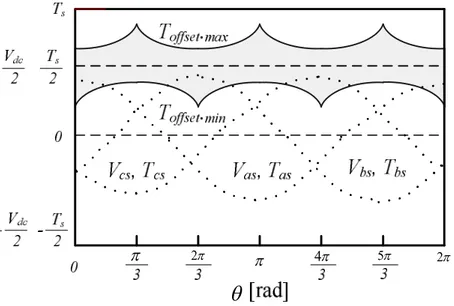

2p 4p 5p 그림 3. 2 가능한 오프셋 시간의 도표(변조지수: 0.9)Fig. 3. 2 Graphical representation range of available offset time (modulation index: 0.9)

이때 유효시간이 한 샘플링 주기의 중간에 위치해야 한다는 조건으로부터 다음 식을 얻을 수 있다. min 0

2

1

T

T

T

offset=

-

(3.4) 여기서, eff ST

T

T

0=

-

(3.5) 실제 게이팅 시간은 DC-Link 전압의 완전한 활용을 보장하기 위해 0 에서 Ts 범위로 제한해야 한다:11

ïî

ï

í

ì

£

+

+

£

s offset offsetT

T

T

T

T

max min0

(2.6) 오프셋 시간은 다음과 같이 제한된다: max . min . offset offset offsetT

T

T

£

£

(2.7)여기서 Toffset.max와 Toffset.min은 Toffset의 최소, 최대값이다.

12

제

4 장 제안된 중성점 전압 제어 기법

4.1 제안된 중성점 전압 제어의 원리

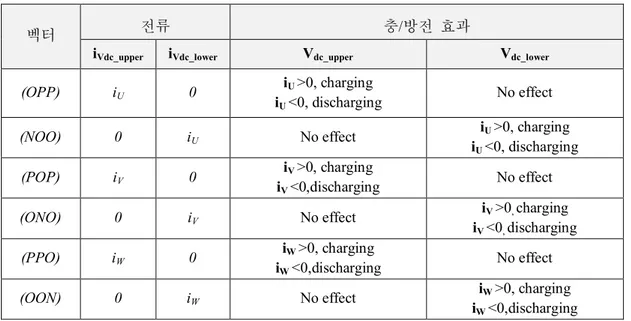

3-레벨 NPC 인버터의 DC-Link 중성점 전압의 불평형을 제어하기 위해서는 중성점을 통해 흐르는 평균 전류(mean current)는 0이 되어야 한다. 이때 중성점을 통해 흐르는 전류는 3상의 부하 상전류의 합으로 표현된다. 즉, 중성점을 통해 흐르는 전류의 극성과 크기를 제어함으로써 3-레벨 NPC 인버터의 DC-Link 중성점 전압을 제어 할 수 있다. 이에 그림 4. 1에 몇 가지 벡터들을 예를 들어, 중성점에 흐르는 전류에 의해 상단 및 하단 커패시터의 충·방전되는 현상을 나타내었다. 그림 4. 1 (a)는(OPP) 벡터일 때의 상태를 보여주고 있다. (OPP) 벡터 상태에서는 U상을 통해 흐르는

전류가 DC-Link 상단 커패시터의 충∙ 방전에 영향을 미치는 것을 알 수 있다

표 4. 1 DC-Link 상단 및 하단 커패시터의 충/방전 효과

Table 4. 1 Charging/Discharging effect on two DC-Link capacitors

벡터 전류 충/방전 효과

iVdc_upper iVdc_lower Vdc_upper Vdc_lower

(OPP) iU 0 iiU >0, charging

U <0, discharging No effect

(NOO) 0 iU No effect iiU >0, charging

U <0, discharging

(POP) iV 0 iiV >0, charging

V <0,discharging No effect

(ONO) 0 iV No effect iiV >0, charging

V <0, discharging (PPO) iW 0 iiW >0, charging

W <0,discharging No effect

(OON) 0 iW No effect iiW >0, charging

13

그림 4. 1 DC-Link 상단 및 하단 커패시터의 충/방전 효과

Fig. 4. 1 Charging/Discharging effect on two DC-Link capacitors

중성점에서 부하측으로 나가는 전류를 + 전류(iU>0)로 가정하였을 때, U상의 전류가 부하측으로 나가는 전류일 경우 상단 커패시터는 충전될 것이고, 반대로 중성점을 통해 들어오는 전류일 경우 상단 커패시터는 방전될 것이다. (NOO) 벡터의 경우는 (OPP) 벡터와 마찬가지로 U상의 전류가 커패시터의 충·방전에 영향을 미치게 되는 전류이나 하단 커패시터의 충·방전에 영향을 미치게 되는 것을 확인 할 수 있다.

14 즉 U상의 전류가 부하측으로 나가는 방향일 경우 하단 커패시터는 충전되며, 중성점을 통해 들어오는 전류일 경우에는 하단 커패시터가 방전되는 것을 확인할 수 있다. 이처럼 각 벡터마다 DC-Link 상단 및 하단 커패시터의 충·방전에 영향을 미치는 부하 전류가 있음을 확인할 수 있다. 이에 표 4. 1에 몇 가지 벡터를 예를 들어 DC-Link 상단 및 하단 커패시터의 충·방전에 영향을 미치는 부하 전류와 극성을 나타내었다. 제안된 방법은 표에서 정리한 것처럼 DC-Link의 상단 및 하단 커패시터의 충·방전에 영향을 미치는 부하 전류의 극성과 크기를 통해 오프셋 전압을 만들어 내 DC-Link의 중성점 전압을 제어하는 방법이다. 또한 제안된 방법은 기존의 SVPWM 방법을 활용한 것으로써 이 방법은 기준전압에 오프셋 전압을 더하는 방법이다. 오프셋 전압을 더하여도 인버터의 출력전압은 변하지 않으나 중성점 전압 균형에 관여하는 중복 벡터는 변화한다. 여기서 중복 벡터는 공간전압 벡터도의 같은 위치를 점유하고 있는 벡터로서 출력 전압의 크기와 방향은 동일하나 DC-Link 상단 및 하단 커패시터의 전류 및 충/방전 효과에 영향을 주는 벡터이다. 즉, 오프셋 전압을 더함으로써 중복 벡터의 크기를 쉽게 제어 할 수 있다. 중성점 전압을 제어하기 위해 기존에는 중복 벡터가 인가되는 시간을 복잡한 계산과정을 통해 얻을 수 있었다. 하지만 제안된 방식은 오프셋 전압을 더함으로써, 복잡한 계산과정 없이 중복 벡터를 쉽게 조절 할 수 있다.

15

4.2 제안된 중성점 전압 제어의 구현

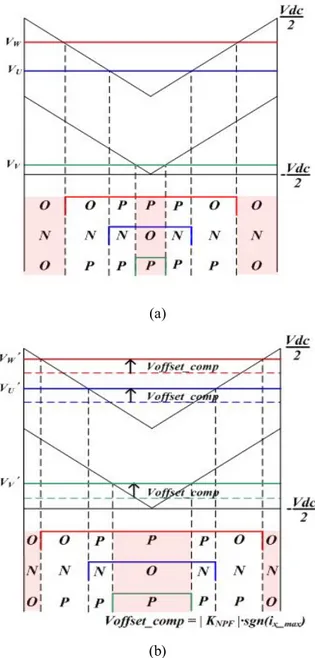

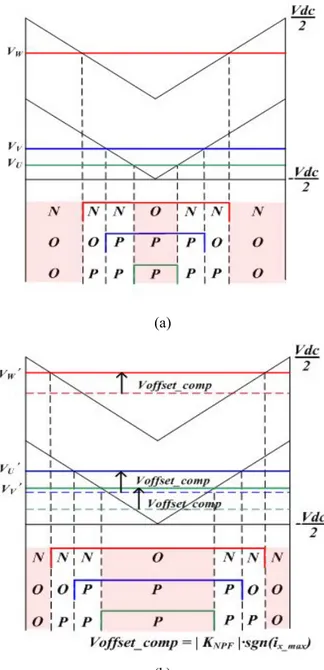

제안된 중성점 전압 제어의 구현을 그림 4. 2와 그림 4. 3을 통해 나타내었다. 그림

4. 2 (a), (b)의 경우, Voffset_comp 을 더해줌으로써 중복 전압 벡터인 (ONO)와 (POP)의 인가

시간이 감소 및 증가됨을 알 수 있으며, 그림 4. 3 (a), (b)의 경우에는 (NOO)와 (OPP)

중복 전압 벡터의 인가 시간이 각각 감소 및 증가됨을 확인 할 수 있다. 비록 중복 전압 벡터의 인가 시간을 변화하나 모두 공간벡터도상의 같은 위치를 점유 하므로 Voffset_comp 에 의한 출력 전압 변동은 나타나지 않는다. 오프셋 전압을 더하였을 때 기준전압이 삼각파인 반송파(carrier) 전압의 최대 범위를 넘어서면 안되기 때문에 오프셋 전압의 범위 또한 정해 줘야 한다. 오프셋 전압의 최대, 최소 범위를 구하게 되면 다음과 같다: max min

2

2

V

V

V

V

V

dc offset dc-

£

£

--

(4.1) 중성점 변동 파라미터 KNPF를 다음과 같이 정의한다.(

)

dc c dc c dc NPFV

V

V

V

V

K

21

2

22

/

2

/

-

=

-=

(4.2) KNPF는 DC-Link 전압의 절반인 Vdc/2에 대한 중성점 전압의 변동이다. KNPF는 측정할 수 없는 양이며, DC-Link 전압 Vdc의 크기와 독립적인 것이다. KNPF의 최대허용 값은 KNPF.max이다. KNPF는 중성점 전압 제어 설계에 대한 입력 변수로 사용된다. 제안된 방법의 오프셋은 다음과 같다:)

sgn(

_max _comp NPF x offsetK

i

V

=

×

(4.3)16 (a)

(b)

그림 4. 2 Voffset_comp 주입과 전압 벡터 인가시간 변화 Ⅰ

: (a) 중복벡터 (ONO), (POP)인가 시간 (b) 중복벡터 (ONO), (POP)인가 시간 변화

Fig. 4. 2 The duration time of the redundancy vector and the added Voffset_comp Ⅰ

: (a) Redundancy vector (ONO), (POP) duration time

17 (a)

(b)

그림 4. 3 Voffset_comp 주입과 전압 벡터 인가시간 변화 Ⅱ

: (a) 중복벡터 (NOO), (OPP)인가 시간 (b) 중복벡터 (NOO), (OPP)인가 시간 변화

Fig. 4. 3 The duration time of the redundancy vector and the added Voffset_comp Ⅱ

: (a) Redundancy vector (NOO), (OPP) duration time

18

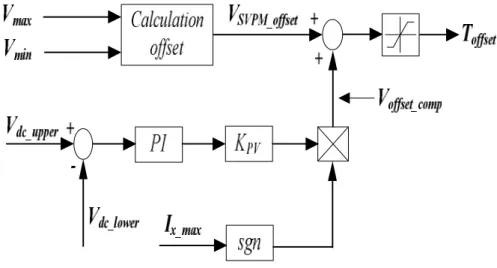

그림 4. 4 제어 블록 다이어그램 Fig. 4. 4 Control block diagram

여기서 , sgn(ix_max)은 최대 전류의 극성으로 정의된다. 그림 4. 4는 제안한 DC-Link 전압 제어 알고리즘의 구현을 보여주고 있다. Voffset_comp은 정현파 PWM 기법의 출력 기준 상전압의 최대, 최소값으로부터 1차적으로 계산된 후, DC-Link 전압 변동량을 입력으로 하는 PI 제어기의 출력과 부하전류 중 최대 크기를 갖는 전류의 극성을 고려하여 최종적으로 결정 된다. 여기서 Kpv는 비례제어 이득(gain)이다.

19

제

5 장 시뮬레이션 및 실험 결과

5.1 시뮬레이션

그림 5. 1 3-레벨 NPC 인버터의 시뮬레이션 모델 Fig. 5. 1 Simulation model of 3-level NPC inverter

제안한 설계를 입증하기 위해, PSIM 프로그램을 이용하여 시뮬레이션을 수행하였다. 3-레벨 NPC 인버터는 R-L부하를 이용하여 구성하였다. 파라메터 값은 다음과 같다. DC-Link 전압과 커패시터는 각각 Vdc=380[V], C=1100[uF]이다. 인버터는 R-L선형 부하에서 동작시켰으며, R=5[Ω ] 그리고 L=10[mH]이며, 스위칭 주파수는 10[kHz]이다. 그림 5. 2에서는 제안한 DC-Link 전압 제어가 적용되지 않았을 때의 시뮬레이션 결과이다. DC-Link 전압 제어가 이루어 지지 않아 DC-Link 중성점 전압의 불평형을 확인 할 수 있다. 즉, 두 커패시터 간에 걸리는 전압 Vdc_upper, Vdc_lower 사이에 평형을 이루지 못하고 발산하는 것을 확인 할 수 있다.

20 그림 5. 3에 제안한 DC-Link 전압 제어 시뮬레이션 결과를 보여주고 있다. t=0.15s 이전에 제안된 중성점 전압 제어는 동작하지 않으며 DC-Link 중성점 전압은 불평형을 보이고 있다. t=0.15s 이후 제안된 중성점 전압 제어가 동작한다. 그림 5. 3(a)는 PI 제어기를 적용하지 않은 경우로 제안된 중성점 전압 제어가 동작하기 전인 t=0.15s 이전에는 DC-Link 중성점 전압의 불평형을 확인 할 수 있다. 하지만 중성점 전압 제어를 시작하여 Voffset_comp이 더해진 t=0.15s 이후 DC-Link 중성점 전압의 불평형이 감소됨을 확인 할 수 있다. 하지만 DC-Link의 상단 및 하단 커패시터간의 전압 사이에 진동이 있음을 확인할 수 있다. 그림 5. 3(b)에서는 PI 제어기를 적용하여 제안된 중성점 전압 제어를 하였을 때의 시뮬레이션 결과를 보여주고 있다. 제안된 중성점 전압 제어가 동작하기 전인 t=0.15s 이전에는 DC-Link 중성점 전압의 불평형을 확인할 수 있다. 하지만 중성점 전압 제어가 동작하기 시작하여 Voffset_comp이 더해진 t=0.15s 이후에는 DC-Link 중성점 전압의 불평형이 감소됨을 확인 할 수 있다. 또한 PI 제어기를 적용하여 중성점 전압 제어를 하였을 경우 PI 제어기를 적용하지 않았을 때 보다 좀 더 빠르게 DC-Link의 중성점 전압이 제어되고 DC-link의 상단 및 하단 커패시터 전압 사이의 진동 또한 작음을 확인할 수 있다. 그림 5. 4 에서는 제안된 중성점 전압 제어를 사용하였을 때의 각 상의 출력 선간 전압을 보여주고 있다. 그림 5. 4(a)는 PI 제어기를 적용하지 않은 경우로 출력 선간 전압 VUV, VVW, VWU는 3-레벨로 보여지고 있다. 하지만 상단 및 하단 커패시터에 걸리는 전압 Vdc_upper, Vdc_lower 사이에 전압 진동을 확인할 수 있다. PI 제어기는 상단 및 하단 커패시터 간의 전압 진동을 제어하기 위해 적용되었다. 또한 PI 제어기를 적용한 그림 5. 4(b)는 PI제어기를 적용하지 않은 그림 5. 4(a)와 비교하여 두 커패시터 간의 전압 진동이 적음을 확인할 수 있다.

21

그림 5. 2 중성점 전압 제어를 고려하지 않은 시뮬레이션 결과

22 (a) (b) 그림 5. 3 PI 제어기 유/무에 따른 중성점 전압 변동 시뮬레이션 결과(DC-Link 전압 및 제안된 offset) : (a) PI 제어기가 없는 경우 (b) PI 제어기가 있는 경우

Fig. 5. 3 Simulation results of the neutral point voltage fluctuation with or without PI controller (DC-Link voltage and the proposed Voffset_comp)

: (a) without PI controller (b) with PI controller

23 Vdc_upper Vdc_lower VUV VVW VWU (a) (a) (b) Vdc_upper Vdc_lower VUV VVW VWU (b) 그림 5. 4 PI 제어기 유/무에 따른 중성점 전압 제어 시뮬레이션 결과(DC-Link 및 선간 전압) : (a) PI 제어기가 없는 경우 (b) PI 제어기가 있는 경우

Fig. 5. 4 Simulation results of the neutral point voltage fluctuation with or without PI controller (DC-Link voltage and the line-to-line voltage)

: (a) without PI controller (b) with PI controller

24

5.2 실험 결과 및 검토

제안한 기법을 검증하기 위하여 3,500rpm급 2.2kW 유도 전동기 MG 구동 시스템을 이용하였다. 제어보드는 TI사의 DSP TMS320F28335로 구성하였다. 그림 5. 5는 전체적인 실험 구성도를 나타내고 있다. 실험에 사용된 유도 전동기의 사양은 표 5. 1과 같다. 제안한 기법의 유효성을 입증하기 위해 그림 5. 6과 같이 인위적인 불평형 오프셋 전압을 인가하였다. 그 결과 약 51.6[V]의 Link 전압 차이를 확인 할 수 있다. DC-Link 전압 차로 인해 정상적인 3-레벨 출력 선간 전압이 아님을 확인 할 수 있다. 그림 5. 7과 그림 5. 8은 무부하 40Hz에서 초기에 인위적인 불평형 오프셋 인가 후 제안한 중성점 평형 오프셋을 보상한 실험 결과이다. Vdc_upper는 상단 커패시터에 인가되는 전압이며, Vdc_lower는 하단 커패시터에 인가되는 전압이다. Voffset_comp는 제안한 중성점 평형을 위한 오프셋 전압이며, DAC 출력을 통해 확인 할 수 있다. 인위적인 불평형 오프셋 인가 시 약 51[V]의 상단 및 하단 커패시터의 전압 차를 확인 할 수 있고, 그 때의 출력 선간 전압(V_UV)은 상단 및 하단 커패시터에 인가되는 전압 차로 인해 정확한 3-레벨 출력 선간 전압이 아님을 확인할 수 있다. 제안한 중성점 평형 오프셋 인가 후 점차적으로 DC-Link 전압 차가 줄어듦을 확인할 수 있고 정상적인 3-레벨 출력 선간 전압과 정현적인 전류(I_U) 파형을 확인 할 수 있다. 그림 5. 9와 5. 10은 무부하 50Hz에서의 실험 결과이며, 위의 실험 방법과 동일하게 인위적으로 불평형 오프셋을 인가하여 상단 및 하단 커패시터에 인가되는 전압차를 만든 후 제안한 중성점 평형을 위한 오프셋을 인가하였다. 중성점 전압 평형을 위한 오프셋 인가 후 DC-Link 전압 차가 없고 정상적인 출력 선간 전압과 정현적인 출력 상 전류를 확인할 수 있다. 그림 5. 11과 그림 5. 12는 무부하 60Hz에서의 실험결과이다. 앞의 실험들과 마찬가지로 제안한 중성점 평형을 위한 오프셋 인가 후 상단 및 하단 커패시터에 인가되는 전압차가 줄어듦을 확인할 수 있다. 그림 5. 13은 부하조건에서의 실험 결과로 시뮬레이션 결과와 유사함을 확인할 수 있고 이를 통해 제안한 DC-Link 중성점 전압 제어 기법이 유효함을 확인 할 수 있다.25

그림 5. 5 3-레벨 NPC 인버터 실험 세트

Fig. 5. 5 The tests set up for three-level NPC inverter

표 5. 1 유도전동기의 정격과 파라미터

Table 5. 1 Specification of induction motor used in experiment

극수 2 pole 고정자 저항 0.84[Ω] 회전자 저항 0.9714 [Ω] 고정자 인덕턴스 0.0054 [H] 회전자 인덕턴스 0.00422[H] 상호 인덕턴스 0.228[H]

26

그림 5. 6 불평형 오프셋 인가 후 상/하단 커패시터 전압 및 출력 선간 전압.

Fig. 5. 6 Vdc_upper, Vdc_lower and line-to-line voltage after added the unbalance offset

그림 5. 7 제안한 공간 벡터 PWM 기법을 적용한 무부하 40Hz 실험 결과

27 (a) (b) 그림 5. 8 제안한 공간 벡터 PWM 기법의 실험 결과 (무부하, 40Hz) : (a) DC-Link 전압 및 출력 선간 전압 (b) DC-Link 전압 및 출력 상 전류

Fig. 5. 8 Experiments result of the proposed space vector PWM method (No load, 40Hz) : (a) DC-Link Voltage and line-to-line voltage

28

그림 5. 9 제안한 공간 벡터 PWM 기법을 적용한 무부하 50Hz 실험 결과

29 (a) (b) 그림 5. 10 제안한 공간 벡터 PWM 기법의 실험 결과 (무부하, 50Hz) : (a) DC-Link 전압 및 출력 선간 전압 (b) DC-Link 전압 및 출력 상 전류

Fig. 5. 10 Experiments result of the proposed space vector PWM method (No load, 50Hz) : (a) DC-Link Voltage and line-to-line voltage

30

그림 5. 11 제안한 공간 벡터 PWM 기법을 적용한 무부하 60Hz 실험 결과 Fig. 5. 11 Experiments result of the proposed space vector PWM method : No load, 60Hz

31 (a) (b) 그림 5. 12 제안한 공간 벡터 PWM 방법의 실험 결과 (무부하, 60Hz) : (a) DC-Link 전압 및 출력 선간 전압 (b) DC-Link 전압 및 출력 상 전류

Fig. 5. 12 Experiments result of the proposed space vector PWM method (No load, 60Hz) : (a) DC-Link Voltage and line-to-line voltage

32

Vdc_upper (20V/div)

Vdc_lower (20V/div)

Voffset_comp

그림 5. 13 제안한 공간 벡터 PWM 기법을 적용한 부하 60Hz 실험 결과

33

제

6 장 결 론

본 논문에서는 3-레벨 중성점 다이오드 클램프(NPC) 인버터의 DC-Link 중성점 전압을 제어하기 위해 간단한 공간벡터 PWM 기법을 제안하였다. DC-Link 중성점 전압을 제어하기 위해 DC-Link 상단 및 하단 커패시터의 충∙방전에 영향을 미치는 부하 전류를 분석하였다. 분석을 바탕으로 DC-Link 상단 및 하단 커패시터의 충∙방전에 영향을 미치는 부하 전류의 극성과 크기를 통해 중복(redundancy) 벡터의 인가 시간을 변화 시키는 오프셋 전압의 관계를 유도하였다. 유도된 오프셋 전압을 통해 DC-Link 중성점 전압을 제어하는 기법을 제안하였다. 또한 제안한 기법은 통합 전압 변조 기술을 기반으로 하고 있다. 기존의 제어 방법은 일정한 DC-Link 중성점 전압을 유지한다고 하더라도 복잡한 계산 과정이 필요하였다. 하지만 제안한 기법은 복잡한 계산 과정이 생략되고 DC-Link 중성점 전압 제어 요소를 내포하는 계산되어진 오프셋 전압을 이용하였다. 본 논문에서 제안한 기법의 타당성을 검증하기 위해 시뮬레이션과 실험을 수행하였다. 먼저 제안한 DC-Link 중성점 전압 제어의 유효함을 비교 검증하기 위해 DC-Link 중성점 전압 제어를 적용하지 않은 경우의 시뮬레이션을 통해 DC-Link 상단 및 하단 커패시터에 인가되는 전압이 평형을 이루지 않고 발산되는 것을 확인 하였다. 이후 제안한 DC-Link 중성점 전압 제어 기법을 적용한 시뮬레이션을 수행하였다. PI 제어기 유/무에 따라 2가지 경우로 시뮬레이션을 수행하였고, PI 제어기를 적용하였을 경우 DC-Link 상단 및 하단 커패시터에 인가되는 전압 사이의 진동이 적을 뿐 더러 조금 더 빠르게 DC-Link 중성점 전압 제어가 이루어짐을 확인 하였다.34 본 논문에서 제안한 방법의 타당성을 검증하기 위해 유도 전동기를 이용하여 실험을 수행하였다. 우선 무부하 상태에서 인위적으로 DC-Link 중성점 전압의 불평형을 만들기 위한 오프셋을 인가하였고 DC-Link 상단 및 하단 커패시터에 인가되는 전압 차이를 확인 하였다. 이 후 제안한 DC-Link 중성점 전압 제어를 위 한 오 프 셋 을 인 가 하 였 고 제 안 한 오 프 셋 인 가 후 D C - Li n k 상 단 및 하 단 커패시터에 인가되는 전압 차이가 줄어듦을 확인 할 수 있었다. 무부하 상태에서의 유효성을 바탕으로 부하 상태에서 제안한 DC-Link 중성점 전압 제어 실험을 수행 하였다. DC-Link 중성점 전압 제어가 적용되지 않았을 때는 DC-Link 상단 및 하단 커패시터에 인가되는 전압 사이에 약 40V 정도의 전압 차이를 확인 할 수 있었다. 하지만 제안한 DC-Link 중성점 전압 제어가 적용된 이 후 DC-Link 상단 및 하단 커 패 시 터 에 인 가 되 는 전 압 차 가 줄 어 듦 을 확 인 할 수 있 었 다 . 제안한 기법은 기존의 DC-Link 중성점 전압 제어를 위해 수행 하였던 복잡한 계산 과정을 생략하였다. 또한 인버터의 출력전압 변동에 영향을 미치지 않고 DC-Link 중성점 전압 평형에 영향을 미치는 중복 벡터에 계산되어진 오프셋 전압을 인가함으로써 복잡한 계산 과정 없이 중복 벡터를 쉽게 조절 하였다. 제안한 기법은 시뮬레이션과 실험 결과를 통해 확인 하였고 DC-Link 중성점 전압 제어가 상당히 개선됨을 입증하였다.

35

참

고 문 헌

[1] C. Newton and M. Sumner, “Neutral point control for multi-level inverters: Theory, design and operational limitations,” in Proc. Ind. Appl. Soc. (IAS), New Orleans, LA, Oct. 1997, vol. 2, pp. 1336–1343.

[2] K. R. M. N. Ratnayake, Y. Murai, and T. Watanabe, “Novel PWM scheme to control neutral point voltage variation in three-lever voltage source inverter,” in Conf. Rec. IEEE-IAS Annu.

Meeting, 1999, pp. 1950–1955.

[3] Y.-H. Lee, R.-Y. Kim, and D.-S. Hyum, “A novel SVPWM strategy considering dc-link balancing for a multi-level voltage source inverter,” in Proc. IEEE APEC’99, 1999, pp. 509–514.

[4] S. Ogasawara and H. Akagi, “Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters,” in Conf. Rec. IEEE-IAS Annu. Meeting, 1993, pp. 965–970.

[5] X. Yuan and I. Barbi, “Soft-switched three level capacitor clamping inverter with clamping voltage stabilization,” in Conf. Rec. IEEE-IAS Annu. Meeting, 1999, pp. 502–508.

[6] K. Yamanaka, A.M. Hava, H. Kirino, Y. Tanaka, N. Koga, T. Kume, "A novel neutral point potential stabilization technique using the information of output current polarities and voltage vector", IEEE Transactions on Industrial Applications, Vol. 38, no. 6, pp.1572-1580, Nov/Dec 2002.

[7] S. Busquets-Monge, J. Bordonau, D. Boroyevich, and S. Somavilla, “The nearest three virtual space vector pwm—Amodulation for the comprehensive neutral-point balancing in the three-level npc inverter,” IEEE Power Electron. Lett., vol. 2, no. 1, pp. 11–15, Mar. 2004.

[8] N. Celanovic and D. Boroyevich, “Acomprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters,” IEEE Trans.

36

[9] J. Pou, J. Zaragoza, P. Rodríguez, S. Ceballos, V. Sala, R. Burgos, and D. Boroyevich, “Fast-processing modulation strategy for the neutralpoint-clamped converter with total elimination of the low-frequency voltage oscillations in the neutral point,” IEEE Trans. Ind.

Electron., vol. 54, no. 4, pp. 2288–2299, Aug. 2007.

[10] Dae-Woong Chung, Joohn-Sheok Kim, Seung-Ki Sul, “Unified voltage modulation technique for real-time three-phase power conversion,” IEEE Transactions on Industrial

37

ABSTRACT

A Simple Space Vector PWM Scheme with Neutral Point Balancing for

Three-Level Neutral Point Clamped Inverter

by

Yoon-Hyuk Ko

Under the supervision ofProf. DONG-SEOK HYUN, Ph.D

Dept. of Electrical Engineering The Graduate School Han Yang University

Three-level Diode Clamped Multilevel Inverter, generally known as Neutral-Point-Clamped(NPC) Inverter, has an inherent problem causing Neutral Point(NP) potential variation. Until now, in many literatures NP potential problem has been investigated and lots of solutions have been proposed. In this paper, a simple control scheme based on the unified voltage modulation technique has been proposed to balance the neutral-point voltage of three-level NPC inverter. The proposed scheme has been achieved by the calculated off-set voltage including the neutral point balancing factor. The neutral point fluctuation can be simply compensated without additional efforts and easily applied to the unified voltage modulation. The validity of the proposed scheme has been proven through the simulation and experiments results.

38

감사의

글

전력전자에 대한 기대를 안고 한양대학교 전력전자 연구실에 입학하고 우여곡절 끝에 많은 분들의 도움으로 이제서야 졸업을 앞두게 되었습니다. 당시 연구실에서의 2 년이라는 시간은 저에게 있어 기나긴 시간으로만 느껴졌지만 사회생활을 하다보니 연구실에의 2 년은 정말 짧게만 느껴졌습니다. 대학원 생활을 하면서 조금 더 노력하고 공부했더라면 더 많은 것을 배울 수 있었는데 제 부족함으로 인해 좋은 기회를 놓친 것 같아 아쉬울 따름입니다. 그래도 늦게나마 석사과정을 마칠 수 있도록 도움을 주신 여러분들께 감사의 말을 전하고 합니다. 가장 먼저 저에게 전력전자 학문의 길을 열어주시고 가장 좋은 연구 환경을 갖춰 연구에 매진할 수 있도록 지도해 주시고 이끌어 주신 현동석 교수님께 감사의 말씀을 드립니다. 그리고 열정적인 강의와 가르침으로 많은 것을 배울 수 있게 지도 해주신 김래영 교수님께도 감사의 말씀 드립니다. 아울러 바쁘신 와중에도 부족한 저의 논문을 심사해 주시고 부족한 부분을 일깨워 주신 정진욱 교수님께도 감사의 말씀 드립니다. 그리고 졸업하신 선배님들께 감사의 말씀을 드립니다. 제가 석사과정을 마칠 수 있도록 큰 도움을 주신 병건이형. 지면으로 감사의 말씀을 드리기에는 부족하기에 연락드리도록 하겠습니다. 그리고 미국에 계신 귀준이형. 형의 많은 가르침 또한 잊지 않고 감사드립니다. 박사 졸업을 앞두신 창순 선배께도 감사 말씀드립니다. 회사생활도 연구실 생활만큼 충분히 잘 하실꺼라 믿어 의심치 않습니다. 그리고 박사과정 중인 민섭이형. 형이 있어서 연구실 생활이 즐거웠습니다. 그리고 2 년동안 동거동락한 나의 소중한 동기들. 너무나도 명석한 두뇌를 갖고 있고 멀티레벨39 인버터라는 한 배를 타고 나에게 너무 큰 도움을 준 남준이. 남은 박사과정 무사히 마치길 바랄께. 운동도 잘하고 분위기 메이커였던 상욱이. 위치해 있는 자리에서 제 몫 해내고 있으리라 믿어 의심치 않아. 그리고 용욱이형, 홍주형, 기영이, 상수형, 재훈이, 태훈이형, 일권이, 준호형께도 감사의 말 전합니다. 그리고 많은 도움 준 동엽이. 너무 고맙고 좋은 소식있을꺼라 믿어 의심치 않아. 이 외에도 연구실 내 많은 후배님들께도 감사의 말 전합니다. 마지막으로 사랑하는 가족들에게 감사의 말씀 전합니다. 지금의 제가 있기 까지 뒤에서 묵묵히 믿고 뒷바라지 해주신 아버지, 어머니. 표현이 서툴고 멀리 떨어져 있어서 자주 찾아 뵙지 못하지만 마음만큼은 항상 곁에 있습니다. 든든한 아들이 될 수 있도록 더 노력하겠습니다. 아버지, 어머니 사랑합니다. 그리고 저의 하나뿐인 누나. 동생인 저에게 항상 양보하고 배려하다 보니 본인 욕심은 채우지 못했는데 고마운 마음과 미안한 마음을 장난으로만 서툴게 표현하는 저를 항상 믿어줘서 고마워. 앞으로 더 잘 할께. 2014 년 6 월 20 일 고 윤 혁