고출력 LED 패키지의 Thermal Via 형성을 위한 Si 기판의 이방성 습식식각 공정

유병규·김민영·오태성† 홍익대학교 공과대학 신소재공학과

Anisotropic Wet-Etching Process of Si Substrate for Formation of Thermal Vias in High-Power LED Packages

B. K. Yu, M. Y. Kim and T. S. Oh†

Department of Materials Science and Engineering, Hongik University, Seoul 121-791, Korea (2012년 12월 18일 접수: 2012년 12월 24일 수정: 2012년 12월 26일 게재확정)

초 록: 습식공정으로 thermal via용 SI 관통 via를 형성하기 위해 TMAH 용액의 농도와 온도에 따른 Si 기판의 이방성 습식식각 거동을 분석하였다. TMAH 용액의 온도를 80oC로 유지한 경우, 5 wt%, 10 wt% 및 25 wt% 농도의 TMAH 용액은 각기 0.76 µm/min, 0.75 µm/min 및 0.30 µm/min의 Si 식각속도를 나타내었다. 10 wt% TMAH 용액의 온도를 20oC와 50oC 로 유지시에는 각기 0.07 µm/min와 0.23 µm/min으로 식각속도가 저하하였다. Si 기판의 양면에 동일한 형태의 식각 패턴을 형성하여 80oC의 10 wt% TMAH 용액에 장입하고 5시간 식각하여 깊이 500 µm의 관통 via hole을 형성하였다.

Abstract: In order to fabricate through-Si-vias for thermal vias by using wet etching process, anisotropic etching behavior of Si substrate was investigated as functions of concentration and temperature of TMAH solution in this study. The etching rate of 5 wt%, 10 wt%, and 25 wt% TMAH solutions, of which temperature was maintained at 80oC, was 0.76µm/min, 0.75 µm/

min, and 0.30µm/min, respectively. With changing the temperature of 10 wt% TMAH solution to 20oC and 50oC, the etching rate was reduced to 0.067µm/min and 0.233 µm/min, respectively. Through-Si-vias of 500 µm-depth could be fabricated by etching a Si substrate for 5 hours in 10 wt% TMAH solution at 80oC after forming same via-pattern on each side of the Si substrate.

Keywords: LED, anisotropic wet etching, thermal via, through-Si-via, TMAH

1. 서 론

발광 다이오드(light emitting diode, LED)는 친환경, 낮 은 소비전력, 뛰어난 색 재현성, 긴 수명 등의 장점을 바 탕으로 기존의 광원을 대체할 차세대 광원으로 큰 주목 을 받고 있다.1-3) LED는 반도체 소자의 일종으로써 기존 의 필라멘트를 사용하는 백색 광원에 비해 높은 효율성 과 신뢰성을 가지기 때문에, 휴대전화 기판을 시작으로 LCD TV의 백라이트 조명장치나 자동차의 헤드라이트 등을 거쳐 현재는 일반조명 분야에 이르기까지 점점 그 활용 범위가 확대되고 있다.4,5) LED를 일반 조명에 적용 하기 위해서는 LED소자의 고출력화가 필수적이기 때문 에, 수십~수백 W급의 고출력 LED 개발에 대해 국내외적 으로 많은 연구가 진행되고 있다.2,5)

고출력 LED소자의 경우 출력 전압이 높아짐에 따라 그 에 비례하여 LED 소자의 p-n 접합부에서 발생하는 열이 증가하며, 이 열이 내부에서 지속적으로 유지될 경우 LED 소자의 온도가 상승하여 광방출 효율이 감소되는 문 제가 발생하게 된다.5,6) 또한 발생된 열이 장기간 지속되 면 LED 소자의 색재현성이나 수명을 감소시키는 요인이 되어 LED 소자의 신뢰성이 저하되게 된다.7) 따라서 고 출력 LED 소자의 개발을 위해서는 소자에서 발생한 열 을 외부로 원활히 방출할 수 있는 방열 방안에 대한 연구 개발이 필수적으로 요구된다.8,9)

현재 고출력 LED의 방열 패키지 방안으로는 우수한 열 전도도 특성을 지닌 MPCB(metal printed circuit board) 위 에 LED 칩을 실장하여 열을 분산시키는 방법,5,9,10) LED 칩이 실장되는 패키지 자체를 금속으로 제작하여 방열특

†Corresponding author E-mail: ohts@hongik.ac.kr

© 2012, The Korean Microelectronics and Packaging Society

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/

licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

성을 향상시키는 방법,11) 패키지의 하단부에 열전도도가 우수한 구리 등의 금속으로 제작된 heat sink를 부착하여 이를 통해 열을 방출시키는 방법5,12)이 사용되고 있다. 그 러나 이와 같은 방열 패키지들은 고가의 비용이 발생하 거나 구조적으로 큰 부피를 차지하거나, 무게가 무겁다 는 문제점들이 있다.5) 이와 같은 문제점들을 해결하기 위 해 MPCB보다 가격이 저렴하고 Cu보다 가벼우면서 열전 도도가 우수한 Si을 방열 기판으로 사용한 LED 패키지 가 개발되었으며2,12,13), Si 기판의 방열 특성을 더욱 향상 시키기 위해 Si 기판에 비아(via) hole을 뚫고 이를 Cu로 채운 thermal via 공정이 제안되었다.2,8,14) Cu thermal via용 via hole을 Si 기판에 형성하는 방법은 Deep RIE(reactive ion etching)를 이용한 공정15)과 Si의 이방성 에칭 특성을 이용한 습식식각법으로 대별할 수 있다.16)이방성 습식식 각법은 MEMS 분야에서 Si 기판에 via hole을 형성할 때 주로 사용하는 방법으로 Deep RIE에 비해 공정이 단순하 여 공정단가가 저렴하며, 큰 부피를 갖는 via hole을 손쉽 게 제작할 수 있다는 장점이 있다.17,18)

본 연구에서는 Cu thermal via를 구비한 고출력 LED 패 키지용 방열 기판을 개발하기 위한 기초 연구로서 습식식 각 공정변수에 따른 Si의 습식식각 특성을 분석 후, 이방 성 습식식각법으로 Si 기판에 관통 via hole을 형성하였다.

2. 실험 방법

이방성 습식식각으로 via hole들을 형성하기 위한 Si 기 판으로는 boron이 도핑된 p-type (100) Si 웨이퍼를 사용 하였다. 식각 마스크로는 Si 식각용액에 대해 식각 선택 도가 우수한 SiO2를 1000Å 두께로 열 성장시켜 사용하 였으며, SiO2 층을 성장시킨 Si 기판에 포토리소그래피 공정을 사용하여 정사각형 형태의 포토레지스트 식각 패 턴을 형성하였다. 식각 패턴으로는 100 µm×100 µm, 300µm ×300 µm 및 500 µm×500 µm 크기의 정사각형 형

상의 패턴을 사용하였다. 식각 패턴을 형성한 Si 기판을 BOE (buffered hydrofluoric acid) 용액에 장입하여 식각하 고자 하는 부위의 SiO2를 제거한 후 포토레지스트 패턴 을 제거하여 이방성 습식식각을 위한 Si 기판 시편을 제 작하였다.18,19)

TMAH(tetramethylammonium hydroxide) 용액과 KOH 용액을 사용하여 Si 기판의 식각 거동을 비교 분석한 후, Si 이방성 습식식각을 위한 식각 용액으로 TMAH 용액을 선택하였다. TMAH 용액의 농도에 따른 Si의 식각 특성 을 분석하기 위해 TMAH 25% 용액을 증류수에 희석시 켜 5% 및 10% TMAH 용액을 제조하였다. TMAH 용액 에 SiO2 식각 마스크가 형성된 Si 기판을 장입한 후, 용액 의 온도를 상온에서 80oC까지 변화시키며, TMAH 용액 의 농도와 온도 및 식각 시간에 따른 식각 특성을 분석하 였다. 식각이 진행되는 동안 식각 용액의 온도와 농도를 일정하게 유지하기 위해 식각 용액을 중탕기에 넣고 300 rpm으로 교반하며 식각을 진행하였다.18-20)

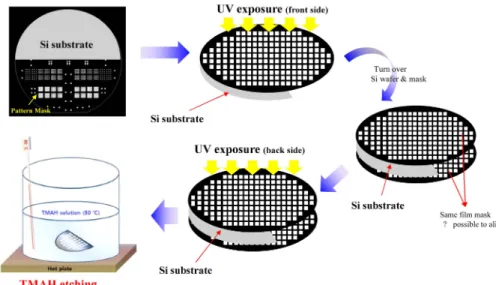

습식식각을 이용해 Si 웨이퍼의 한쪽 면만을 식각하게 되면 V-groove 형태로 식각이 이뤄지기 때문에 관통된 형 태의 via hole을 형성하기 위해서는 Si 웨이퍼의 양면에 동일한 형태와 크기와 간격을 갖는 식각 패턴을 각기 형 성해야 한다. 이를 위해 Fig. 1과 같이 Si 웨이퍼를 절반 으로 절단하고 Si 기판의 양면에 스핀코팅법으로 포토레 지스트 층을 성막하였다. 이와 같은 Si 웨이퍼의 한쪽 면 에 via hole 패턴이 형성된 필름 마스크를 이용하여 노광 및 현상 작업 등의 포토리소그래피 공정을 거쳐 via hole 패턴을 형성하였다. Si 기판의 반대 면에도 동일한 via hole 패턴을 용이하게 형성하기 위해, Si 웨이퍼에 접촉시 킨 필름 마스크가 붙어 있는 채로 via hole 패턴이 형성된 Si 웨이퍼를 뒤집었다. 뒤집은 Si 웨이퍼에 동일한 via hole 패턴의 다른 필름 마스크를 접촉시키고 양면에 있는 필름 마스크들의 via hole 패턴끼리 정렬시킨 후 노광 작 업을 통해 Si 웨이퍼의 반대 면에도 동일한 via hole 패턴

Fig. 1. Schematic illustration for formation of through-Si-via by using anisotropic wet etching of a Si substrate.

을 형성하였다. 양면에 via hole 패턴이 형성된 Si 시편을 TMAH 용액에 넣고 용액의 온도를 80oC로 유지하며 중 탕으로 가열하여 식각시킴으로써 V-groove 형태가 위 아 래로 겹친 모래시계 형태의 via hole을 형성하였다.

식각 공정 후에 α-step surface profiler를 이용하여 via hole의 식각 깊이를 측정하여 식각속도를 계산하였으며, 광학현미경과 주사전자현미경을 사용하여 식각된 via hole 패턴을 관찰하였다.

3. 결과 및 고찰

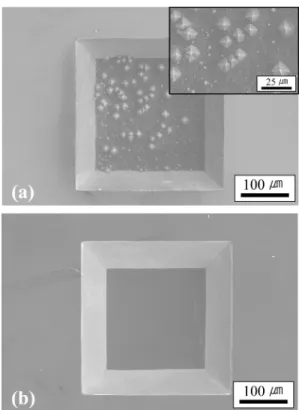

Si의 이방성 습식식각에 더 적합한 식각 용액을 선택하 기 위해, 25 wt% TMAH 용액과 40 wt% KOH 용액을 사 용하여 온도를 80oC로 유지하며 3시간 동안 Si 기판의 식 각을 진행한 후 식각 형상을 관찰하였다. TMAH 용액을 사용하여 식각한 경우에는 Fig. 2(a)와 같이 본래의 via 패 턴 형태가 유지되며 V-groove 형태로 (100)면의 식각이 진행되는 반면에, 40 wt% KOH 용액을 사용한 경우에는 Fig. 2(b)와 같이 본래의 via hole 패턴 이외의 부분도 식 각되어 원형으로 식각이 진행된 것을 관찰할 수 있다.

Fig. 2에서 관찰된 TMAH 용액과 KOH 용액에서 Si의 식 각 거동의 차이는 식각 용액에 따른 Si 결정면의 각기 다 른 식각 속도로 설명될 수 있다. KOH 용액의 경우 (211) 면이나 (311)면과 같은 높은 면지수의 결정면에 대한 식 각이 (100)면에 비해 빠르게 진행되기 때문에 Fig. 2(b)와 같은 식각 거동을 나타내는 것으로 판단된다.21) 이에 비 해 TMAH 용액의 경우 KOH 용액과는 반대로 (100)면의 식각 속도가 다른 면에 비해 높기 때문에 (100)면의 식각 이 우선적으로 진행되어 Fig. 2(a)와 같은 V-groove 형태 로 식각된다.22) Fig. 2의 결과를 바탕으로 via hole 형성을 위한 식각 용액으로 TMAH 용액을 선택하였다.

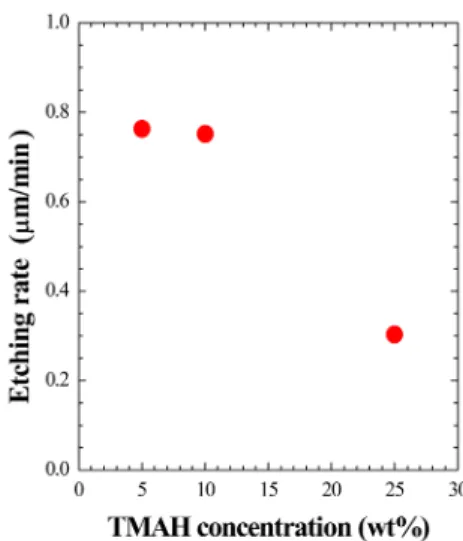

각기 5 wt%, 10 wt% 및 25 wt% 농도의 TMAH 용액의 온도를 80oC로 유지하며 4시간 동안 식각한 Si 기판의 주 사전자현미경 사진을 Fig. 3에 나타내었으며, TMAH 용

액의 농도에 따른 Si 식각 속도를 Fig. 4에 나타내었다. 이 실험에 사용한 via hole 패턴의 크기는 100 µm×100 µm 이 었다. Fig. 4에서와 같이 5 wt%와 10 wt%의 저농도 TMAH 용액을 사용하여 식각한 경우 각기 0.76 µm/min 및 0.75 µm/min의 식각 속도를 나타내었으며, 25 wt%

TMAH 용액에서 식각한 경우에는 이보다 2배 이상 느린 0.30µm/min의 식각 속도를 나타내었다.

Seidel et al.의 식각 공정 모델에 따르면 TMAH 용액과 같은 염기성 용액에 의한 Si의 식각 속도는 식 (1)과 같이 표현할 수 있다.22)

Etching rate ≒ a[H2O]× b[OH-] (1) Fig. 2. Scanning electron micrographs of via holes in a Si substrate

etched by (a) 25 wt% TMAH solution and (b) 40 wt% KOH solution for 3 hours.

Fig. 3. Scanning electron micrographs of via holes in a Si substrate etched by (a) 5 wt%, (b) 10 wt%, and (c) 25 wt% TMAH solutions at 80oC for 4 hours.

Fig. 4. Etching rate of TMAH solution at 80oC as a function of the TMAH concentration.

식 (1)에서 [H2O]는 식각 용액 내 물 분자의 농도, [OH-] 는 식각 용액 내 해리되어 있는 수산화이온의 농도이며, a 와 b는 비례상수이다. 식 (1)과 같이 식각 용액 내 OH- 이 온이 많을수록, H2O의 농도가 클수록 Si의 식각 속도가 증가한다. 식각 용액 내 OH-이온 함량을 증가시키기 위 해 고농도의 식각 용액을 사용할 경우 H2O 분자의 농도 가 감소하기 때문에, 식각 용액의 농도가 증가함에 따라 식각 속도가 증가하다 최대값에 도달한 후 감소하는 거 동을 보이게 된다. 이와 더불어 TMAH 용액의 경우 농도 가 증가할수록 OH- 이온 함량의 증가와 함께 TMA+ 이온 의 함량 또한 증가하게 된다. TMA+ 이온은 Si의 표면에 흡착되어 Si원자와 OH- 이온 간의 반응을 저해하는 요소 로 작용하기 때문에,21-23) 5 wt%와 10 wt% TMAH 용액에 비해 25 wt%의 TMAH 용액에서 Si이 더 느리게 식각되 는 것으로 판단된다.

Fig. 4에서와 같이 5 wt% TMAH와 10 wt% TMAH 용 액의 식각 속도는 각기 0.76 µm/min와 0.75 µm/min로 거 의 유사하였다. 두 용액 간의 보다 정확한 식각 거동의 비 교분석을 위해 식각 용액의 온도를 80oC로 유지시키며 2 시간 동안 식각한 후, 식각 표면을 주사전자현미경으로 관찰하여 Fig. 5에 나타내었다. 두 용액의 거의 유사한 식 각 속도로 인해 Si (100)면의 식각된 깊이는 비슷하였지 만, 식각된 바닥면의 형상에서 차이를 나타내었다. Fig.

5(a)와 같이 5 wt% TMAH 용액으로 식각된 (100)면에서 는 피라미드 형태의 hillock들이 관찰된 반면에, Fig. 5(b) 와 같이 10 wt% TMAH 용액으로 식각한 경우에는 식각

된 (100)면에서 hillock이 관찰되지 않았다. Fig. 5(a)에서 관찰된 피라미드 형상의 hillock들은 <101> 방향의 모서 리로서 식각 용액 내에 분해된 Si의 함량이 증가함에 따 라 {101}면의 식각이 빨라지게 되어 형성되는 것으로 알 려져 있다.20,24) Fig. 4에서와 같이 10 wt% TMAH 용액에 비해 5 wt% TMAH 용액의 경우 식각 속도가 좀더 빠르 나, Fig. 5(a)와 같이 식각된 (100) 바닥면에 hillock이 형 성되는 문제점이 있기 때문에, 5 wt% TMAH 용액은 cantilever 형성과 같은 MEMS 공정에 적용하기에는 적합 하지 않을 것으로 판단된다. 따라서 본 연구에서는 향후 MEMS 공정에의 적용 가능성을 고려하여 via hole 형성 용 식각 용액으로서 10 wt% TMAH 용액을 선택하였다.

TMAH 용액의 온도에 따른 10 wt% TMAH 용액의 식 각 속도의 변화거동을 분석하여 Fig. 6에 나타내었다.

TMAH 용액의 온도 증가에 따라 식각 속도가 크게 증가 하였으며, 이는 Si 표면에 대한 식각 용액의 wetting angle 감소에 기인한다.26) 또한 식각 용액의 온도가 증가함에 따라 용액 내 이온의 확산 속도가 빨라져 식각 용액 내 OH- 이온이 Si 시편의 표면으로 보다 쉽게 확산되며, 식 각반응 물질이 Si 표면에서 용액 내로 빠르게 확산하여 퍼져나갈 수 있기 때문에 Si의 식각 속도가 증가하게 된 다.25) Fig. 6와 같이 TMAH 용액의 온도가 증가할수록 식 각 속도가 증가하지만, TMAH 용액은 25 wt% 농도를 기 준으로 비등점이 100~110oC이기 때문에, 80oC 이상의 온 도에서 용액이 심하게 증발하는 문제가 있어 식각 용액 의 온도는 80oC가 최적 온도로 판단된다.

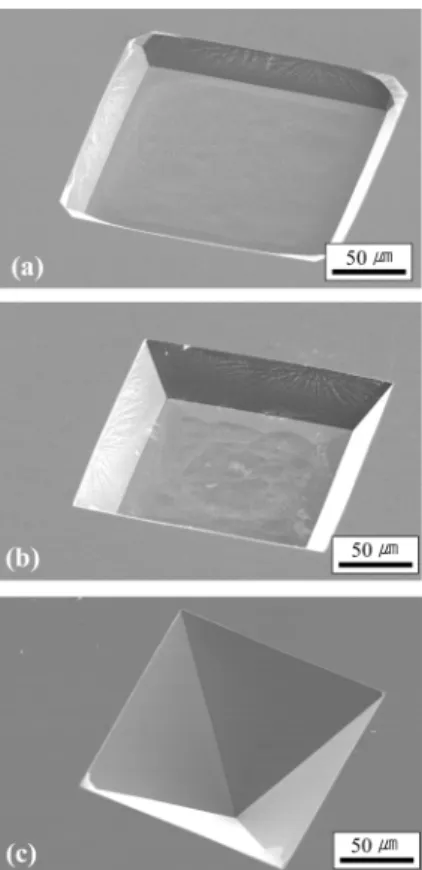

TMAH 용액의 농도를 10 wt%, 온도를 80oC로 고정하 고, 식각 시간에 따른 Si의 식각 진행 거동을 관찰한 주 사전자현미경 사진을 Fig. 7에 나타내었다. 식각 시간이 증가함에 따라 (100)/(111) 면간의 각도인 54.7o를 따라 식 각 패턴의 깊이가 증가하여 Fig. 7(c)와 같이 180분간 식 각을 진행한 경우 깊이 100 µm의 V-groove 형태로 완전 히 식각됨을 관찰하였다.

Fig. 5. Scanning electron micrographs of via holes in a Si substrate etched by (a) 5 wt% and (b) 10 wt% TMAH solutions at 80oC for 2 hours.

Fig. 6. Etching rate of 10 wt% TMAH solution as a function of the etching temperature.

TMAH 용액의 농도와 용액 온도에 따른 실험 결과들로 부터 TMAH 용액의 최적 식각조건은 10 wt% 농도, 용액 온도는 80oC로 결정되었으며, 이 때 Si의 식각 속도는 0.75µm/min이었다. 이와 같은 최적 식각조건을 사용하여 Fig. 1의 공정에 따라 Si 기판에 관통 via hole을 형성하였 으며, 이를 주사전자현미경으로 관찰하여 Fig. 8에 나타내 었다. Fig. 8과 같이 습식 식각으로 형성한 via hole의 한 변의 길이는 Si 표면에서 500 µm 이며, 관통된 via hole의 중심 부분 (bottle neck)에서 가한 변의 길이는 330 µm으 로, Si 기판의 위 아래 면에 있는 via hole 패턴들이 서로

정렬되어 관통 via hole이 형성된 것을 관찰할 수 있다.

TMAH 용액의 최적 식각조건(10 wt% 농도와 80oC의 용액온도)을 사용하여 관통 via hole을 형성시 식각 시간 에 따른 관통 via hole의 형성과정을 관찰한 단면 주사전 자현미경 사진을 Fig. 9에 나타내었다. 식각 시간이 증가 함에 따라 Si 기판 시편의 위 면과 아래 면에 정렬된 식 각 패턴이 TMAH 용액에 의해 동시에 식각되면서, V- groove들이 위 아래로 겹친 모래시계 형상의 깊이 500 µm 인 관통 via hole이 형성되는 것을 관찰할 수 있다.

4. 결 론

(1) 25 wt% TMAH 용액을 사용하여 식각한 Si 기판은 V-groove 형태로 (100)면의 식각이 진행되는 반면에, 40 wt% KOH 용액을 사용한 경우에는 V-groove에서 벗어난 원형으로 식각되어 Si 기판의 이방성 식각공정에 KOH 용액보다 TMAH 용액이 더 적합하였다.

(2) TMAH 용액의 온도를 80oC로 유지한 경우, 5 wt%, 10 wt% 및 25 wt% 농도의 TMAH 용액은 각기 0.76 µm/

min, 0.75µm/min 및 0.30 µm/min의 식각 속도를 나타내 었다. 식각 용액의 농도 증가에 따라 식각 속도가 증가하 다 최대값에 도달한 후 감소하는 일반적인 거동과 비교 시, TMAH 용액의 Si 식각 속도는 5 wt% 부근의 농도에 Fig. 7. Scanning electron micrographs of a via hole in a Si substrate

etched by 10 wt% TMAH solution at 80oC for (a) 50 minutes, (b) 90 minutes, and (c) 180 minutes.

Fig. 8. Scanning electron micrograph of through-Si-vias formed by anisotropic wet etching in 10 wt% TMAH solution at 80oC for 5 hours.

Fig. 9. Cross-sectional scanning electron micrographs of a Si substrate showing progressive formation of through-Si-vias by etching in 10 wt% TMAH solution at 80oC for (a) 1 hour, (b) 3 hours, and (c) 5 hours.

서 최대값을 나타낼 것으로 판단된다.

(3) 10 wt% TMAH 용액으로 식각된 Si (100)면에서는 hillock이 관찰되지 않았으나, 5 wt% TMAH 용액으로 식 각된 (100)면에서는 피라미드 형태의 hillock들이 관찰되 어 5 wt% TMAH 용액은 cantilever 형성과 같은 MEMS 공정에 적용하기에는 적합하지 않을 것으로 판단된다.

(4) TMAH 용액의 온도 증가에 따라 Si 식각 속도가 크 게 증가하였으며, 이는 Si 표면에 대한 식각 용액의 wetting angle 감소 및 식각 용액 내 OH- 이온의 확산 속 도와 식각 반응물질의 확산속도가 증가하는데 기인한다.

(5) Si 기판의 양면에 동일한 형태와 크기 및 간격을 갖 는 식각 패턴을 형성하여 10 wt% TMAH 용액의 온도를 80oC로 유지하며 5시간 동안 식각을 진행함으로써 깊이 500µm의 모래시계 형상의 관통 via hole을 형성하였다.

감사의 글

본 연구는 한국연구재단의 중견연구자지원사업의 지 원으로 수행되었습니다(과제번호 2011-0029443).

참고문헌

1. C. J. Weng, “Advanced Thermal Enhancement and Management of LED Packages”, Inter. Commun. Heat Mass Transfer., 36, 245 (2009).

2. K. Y. Kim and K. K. Ham, “The Technical Trend of Heat Dis- sipation for High Power LED Flood Light”, Proc. KIIEE Spring Conference, Yongpyung, 214, Korean Institute of Illu- minating and Electrical Installation Engineers (2009).

3. S. J. Lee, J. S. Lee and Y. J. Kim, “Synthesis and Optical Properties of M-Si(Al)-O-N (M: Sr, Ca) Phosphors for White Light Emitting Diodes”, J. Microelectron. Packag. Soc., 19(2), 41 (2012).

4. J. Hu, L. Yang and M. W. Shin, “Electrical, Optical and Ther- mal Degradation of High Power GaN/InGaN Light-Emitting Diodes”, J. Phys. D: Appl. Phys. 41, 1 (2008).

5. S. H. Kim, S. I. Lee, J. K. Yang and D. H. Park, “Analysis of Thermal Properties in LED Package by Via-Hole and Dimension of FR4 PCB”, J. KIEEME, 24, 234 (2011).

6. S. Chan and J. S. Jang, “Accelerated Degradation Stress of High Power Phosphor Converted LED Package”, J. Micro- electron. Packag. Soc., 17(4), 19 (2010).

7. J. Park, M. W. Shin and C. C. Lee, “Measurement of Tem- perature Profiles on Visible Light-Emitting Diodes by Use of a Nematic Liquid Crystal and an Infrared Laser”, Optics Lett., 29, 2656 (2004).

8. H. W. Shin, H. S. Lee, J. O. Bang, S. H. Yoo, S. B. Jung and K. D. Kim, “Variation of Thermal Resistance of LED Module Embedded by Thermal Via”, J. Microelectron. Packag. Soc., 17(4), 95 (2010).

9. M. H. Lee, T. J. Lee, H. J. Lee and Y. J. Kim, “Design and Fabrication of Metal PCB Based on the Patterned Anodizing for Improving Thermal Dissipation of LED Lighting”, Proc.

5th Int. Conference on Microsys. Pack. Assembly Circuits Technol., 1, Taipei, IEEE (2010).

10. J. Petroski, “Spacing of High-Brightness LEDs on Metal Sub- strate PCB's for Proper Thermal Performance”, Proc. Intersoc.

Conference Thermal & Thermomech. Phenomena Electron.

Systems, 507, Las Vegas, IEEE (2004).

11. A. Christensen and S. Graham, “Thermal Effects in Packag- ing High Power Light Emitting Diode Arrays”, Appl. Ther- mal Engineer., 29, 364 (2009).

12. M. Arik, C. Becker, S. Weaver and J. Petroski, “Thermal Management of LEDs: Package to System”, Proc. 3th Int.

Conference Solid State Lighting, 64, San Diego, International Society for Optics and Photonics (2004).

13. W. K. Jeung, S. H. Shin, S. Y. Hong, S. M. Choi, S. Yi, Y. B.

Yoon, H. J. Kim, S. J. Lee and K. Y. Park, “Silicon-Based, Multi-Chip LED Package”, Proc. 57th Electron. Comp. Tech- nol. Conference(ECTC), Reno, 722, IEEE CPMT (2007).

14. L. Yang, S. Jang, W. J. Hwang and M. W. Shin, “Thermal Analysis of High Power GaN-Based LEDs with Ceramic Package”, Thermochimica Acta, 455, 95 (2007).

15. K. S. Kim, Y. C. Lee, J. H. Ahn, J. Y. Song, C. D. Yoo and S. B. Jung, “Effect of Process Parameters on TSV Formation Using Deep Reactive Ion Etching”, Korean J. Met. Mater., 48, 1028 (2010).

16. Y. M. Jung and Y. C. Kim, “Fabrication of a (100) Silicon Master Using Anisotropic Wet Etching for Embossing”, J.

Korean Ceram. Soc., 42, 645 (2005).

17. Y. Cao, W. Ning and L. Luo, “Wafer-Level Package with Simultaneous TSV Connection and Cavity Hermetic Sealing by Solder Bonding for MEMS Device”, IEEE Trans. Elec- tron. Pack. Manuf., 32, 125 (2009).

18. C. R. Yang, P. Y. Chen, C. H. Yang, Y. C. Chiou and R. T.

Lee, “Effects of Various Ion-Typed Surfactants on Silicon Anisotropic Etching Properties in KOH and TMAH Solu- tions”, Sens. Actuators A, 119, 271 (2005).

19. K. Biswas, S. Das, D. K. Maurya, S. Kal and S. K. Lahiri,

“Bulk Micromachining of Silicon in TMAH-Based Etchants for Aluminium Passivation and Smooth Surface”, Microelec- tron. J., 37, 321 (2006).

20. P. H. Chen, H. Y. Peng, C. M. Hsieh and M. K. Chyu, “The Characteristic Behavior of TMAH Water Solution for Aniso- tropic Etching on Both Silicon Substrate and SiO2 Layer”, Sens. Actuators A, 93, 132 (2001).

21. I. Zubel and M. Kramkowska, “The Effect of Isopropyl Alco- hol on Etching Rate and Roughness of (100) Si Surface Etched in KOH and TMAH Solutions”, Sens. Actuators A, 93, 138 (2001).

22. H. Seidel, L. Csepregi, A. Heuberger and H. Baumgartel,

“Anisotropic Etching of Crystalline Silicon in Alkaline Solu- tions”, J. Electrochem. Soc., 137, 3626 (1990).

23. I. Zubel, I. Barycka, K. Kotowska and M. Kramkowska, “Sil- icon Anisotropic Etching in Alkaline Solutions IV: The Effect of Organic and Inorganic Agents on Silicon Anisotropic Etch- ing Process”, Sens. Actuators A, 87, 163 (2001).

24. L. M. Landsberger, S. Naseh, M. Kahrizi and M. Paranjape,

“On Hillocks Generated during Anisotropic Etching of Si in TMAH”, J. Microelectromech. Sys., 5, 106 (1996).