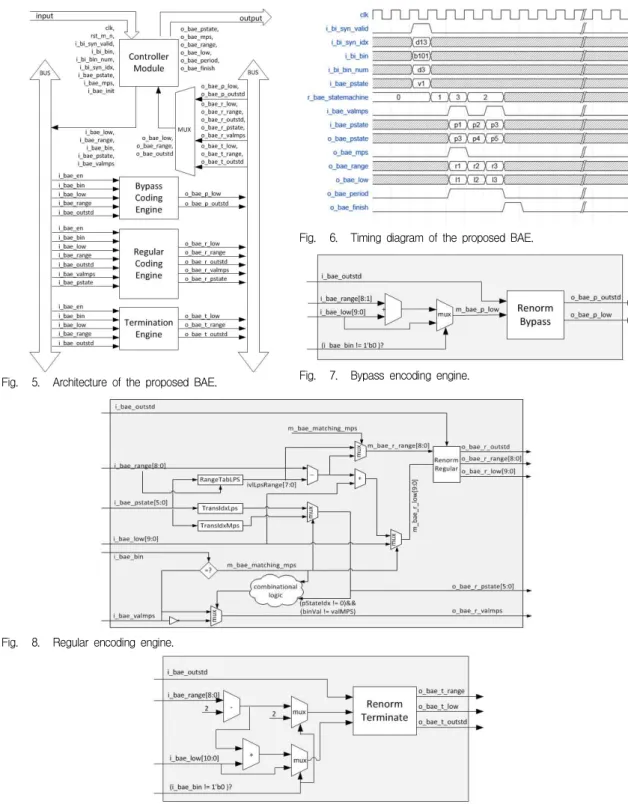

Hardware Implementation of HEVC CABAC Binary Arithmetic Encoder

전체 글

수치

![Fig. 1. Block diagram of HEVC CABAC encoder. (Modified from [5])](https://thumb-ap.123doks.com/thumbv2/123dokinfo/4674847.500976/2.772.69.697.144.830/fig-block-diagram-hevc-cabac-encoder-modified.webp)

관련 문서

Phase Equilibria and Cage Occupancy of Binary Hydrates : Its Application to Gas Hydrate Refrigeration

§ Null-path-length balancing: comparing the null-path-length of each of the two sub-trees (the length to the closest null sub- tree/empty node). § Weight balancing:

aSystem design performs many design tasks at different levels of abstraction.. `Requirements, Specifications, Architecture, Coding,

Electron probe micro-analyzer image of Zr-4%Si binary alloys; (a).. X-ray diffraction profiles of as-cast Zr-xSi binary alloys, which shows the dual phases.. Magnetic

Kernel 1, which has an arithmetic intensity of 0.5 FLOPs/byte, is limited by memory bandwidth to no more than 8 GFLOPS/sec. Kernel 2, which has an arithmetic intensity of

[From Binary Alloy Phase Diagrams, 2nd edition, Vol. Reprinted by permission of ASM International, Materials Park, OH.].. 11.23, Callister & Rethwisch 9e.. [From Binary

[From Binary Alloy Phase Diagrams, 2nd edition, Vol. Reprinted by permission of ASM International, Materials Park, OH.].. 11.23, Callister & Rethwisch 9e.. [From Binary

Q: Why don’t we just use a prime number as our base N since it’s so easy to find the decryptor